ADSP-2186

TIMING PARAMETERS

Parameter |

|

|

|

|

|

| Min | Max |

Clock Signals and Reset |

|

| ||||||

Timing Requirements: |

|

| ||||||

tCKI | CLKIN Period | 60 [50] | 150 | |||||

tCKIL | CLKIN Width Low | 20 |

| |||||

tCKIH | CLKIN Width High | 20 |

| |||||

Switching Characteristics: |

|

| ||||||

tCKL | CLKOUT Width Low | 0.5 tCK – 7 |

| |||||

tCKH | CLKOUT Width High | 0.5 tCK – 7 |

| |||||

tCKOH | CLKIN High to CLKOUT High | 0 | 20 | |||||

Control Signals |

|

|

|

|

|

|

|

|

Timing Requirements: |

|

| ||||||

tRSP | RESET | Width Low1 | 5 tCK |

| ||||

tMS | Mode Setup Before | RESET | High | 2 |

| |||

tMH | Mode Setup After | RESET | High | 5 |

| |||

Unit

ns ns ns

ns ns ns

ns ns ns

NOTES

Parameters displayed inside brackets [ ] represent preliminary 40 MHz specifications.

1Applies after

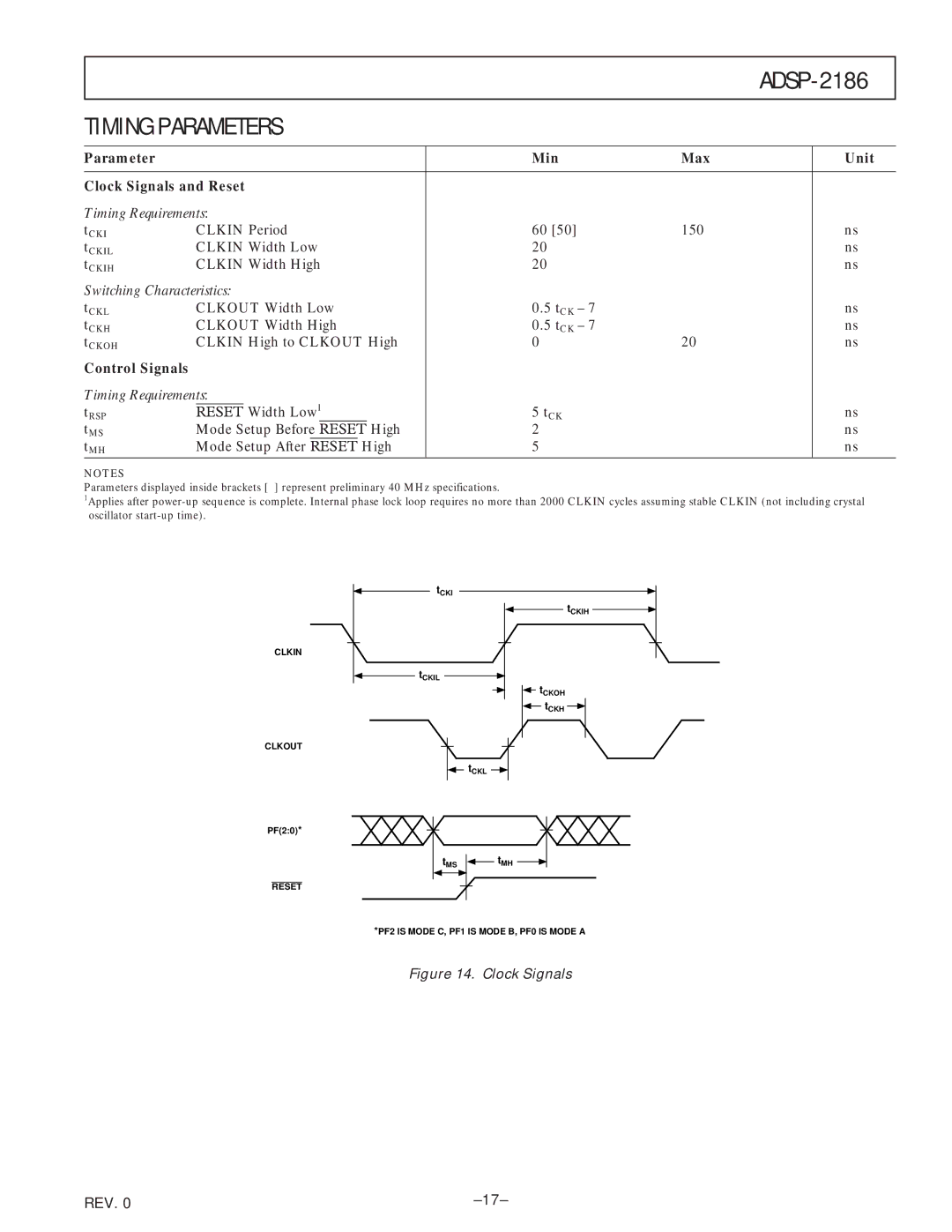

CLKIN

tCKI

tCKIL

tCKIH

tCKOH

tCKH

CLKOUT

PF(2:0)*

RESET

tMS

tCKL ![]()

![]()

tMH

*PF2 IS MODE C, PF1 IS MODE B, PF0 IS MODE A

Figure 14. Clock Signals

REV. 0 |