ADSP-2186

CAPACITIVE LOADING

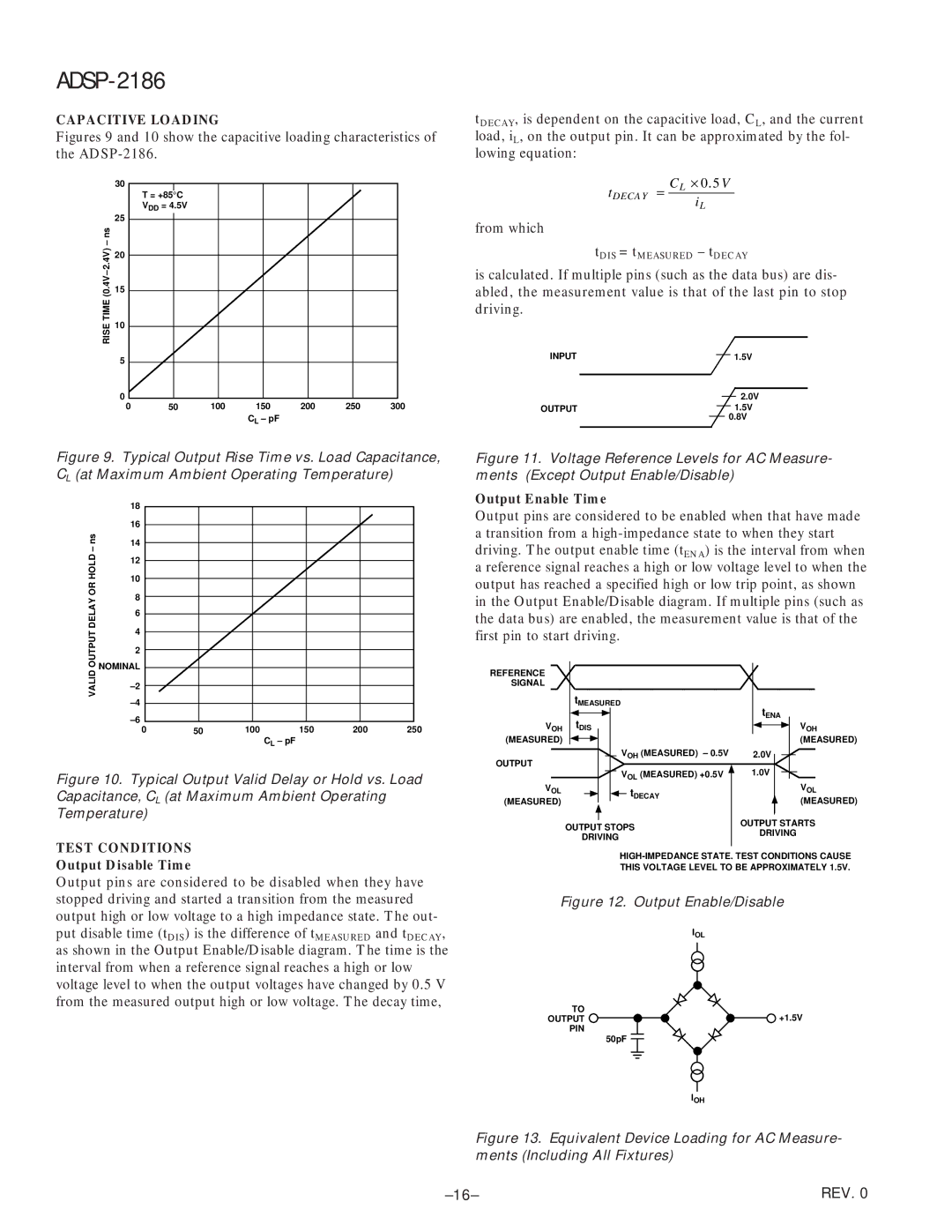

Figures 9 and 10 show the capacitive loading characteristics of the ADSP-2186.

| 30 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

| T = +85 | °C |

|

|

|

|

|

|

|

|

|

|

|

|

| VDD = 4.5V |

|

|

|

|

|

|

|

|

|

| |

– ns | 25 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

2.4V) | 20 |

|

|

|

|

|

|

|

|

|

|

|

|

|

15 |

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

RISE | 10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

| 5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

| 0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

| 0 | 50 | 100 | 150 | 200 | 250 | 300 | |||||||

|

|

|

|

|

|

| CL – pF |

|

|

|

|

|

| |

Figure 9. Typical Output Rise Time vs. Load Capacitance, CL (at Maximum Ambient Operating Temperature)

| 18 | |

| 16 | |

ns | 14 | |

– | ||

| ||

HOLD | 12 | |

| ||

OR | 10 | |

8 | ||

DELAY | ||

6 | ||

| ||

OUTPUT | 4 | |

2 | ||

| ||

VALID | NOMINAL | |

| ||

| ||

|

0 | 50 | 100 | 150 | 200 | 250 |

CL – pF

Figure 10. Typical Output Valid Delay or Hold vs. Load Capacitance, CL (at Maximum Ambient Operating Temperature)

TEST CONDITIONS

Output Disable Time

Output pins are considered to be disabled when they have stopped driving and started a transition from the measured output high or low voltage to a high impedance state. The out-

put disable time (tDIS) is the difference of tMEASURED and tDECAY, as shown in the Output Enable/Disable diagram. The time is the

interval from when a reference signal reaches a high or low voltage level to when the output voltages have changed by 0.5 V from the measured output high or low voltage. The decay time,

tDECAY, is dependent on the capacitive load, CL, and the current load, iL, on the output pin. It can be approximated by the fol-

lowing equation:

tDECAY = CL × 0.5V

iL

from which

tDIS = tMEASURED – tDECAY

is calculated. If multiple pins (such as the data bus) are dis- abled, the measurement value is that of the last pin to stop driving.

INPUT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 1.5V |

| ||||

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

| 2.0V |

| |

|

|

|

|

|

|

|

|

|

|

| ||

OUTPUT |

|

|

|

|

|

|

| 1.5V |

| |||

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

| 0.8V |

| |||||

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

Figure 11. Voltage Reference Levels for AC Measure- ments (Except Output Enable/Disable)

Output Enable Time

Output pins are considered to be enabled when that have made a transition from a

REFERENCE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SIGNAL |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| tMEASURED |

|

|

|

| tENA |

|

|

|

| ||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

VOH | tDIS |

|

|

|

|

|

|

|

|

|

|

|

|

| VOH | ||||||

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

(MEASURED) |

|

|

|

|

|

|

|

|

| VOH (MEASURED) – 0.5V |

| 2.0V |

|

|

| (MEASURED) | |||||

OUTPUT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

| 1.0V |

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

| VOL (MEASURED) +0.5V |

|

|

|

|

|

| |||||

VOL |

|

|

|

|

|

|

|

|

|

| tDECAY |

|

|

|

|

|

|

|

| VOL | |

(MEASURED) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| (MEASURED) | ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| OUTPUT STARTS | |||||||||

| OUTPUT STOPS | ||||||||||||||||||||

|

|

| DRIVING | ||||||||||||||||||

|

|

| DRIVING |

|

| ||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

|

|

|

|

|

|

| ||||||||||||

|

|

|

|

|

|

|

|

|

| THIS VOLTAGE LEVEL TO BE APPROXIMATELY 1.5V. | |||||||||||

Figure 12. Output Enable/Disable

IOL

TO

OUTPUT ![]()

![]()

![]()

![]()

![]() +1.5V PIN

+1.5V PIN

50pF

IOH

Figure 13. Equivalent Device Loading for AC Measure- ments (Including All Fixtures)

REV. 0 |