ADSP-2186

To minimize power consumption during

Interrupts

The interrupt controller allows the processor to respond to the eleven possible interrupts and reset with minimum overhead.

The

PF7:4 pins). In addition, SPORT1 may be reconfigured for IRQ0, IRQ1, FLAG_IN and FLAG_OUT, for a total of six

external interrupts. The

rupt levels are internally prioritized and individually maskable (except

input pins can be programmed to be either level- or

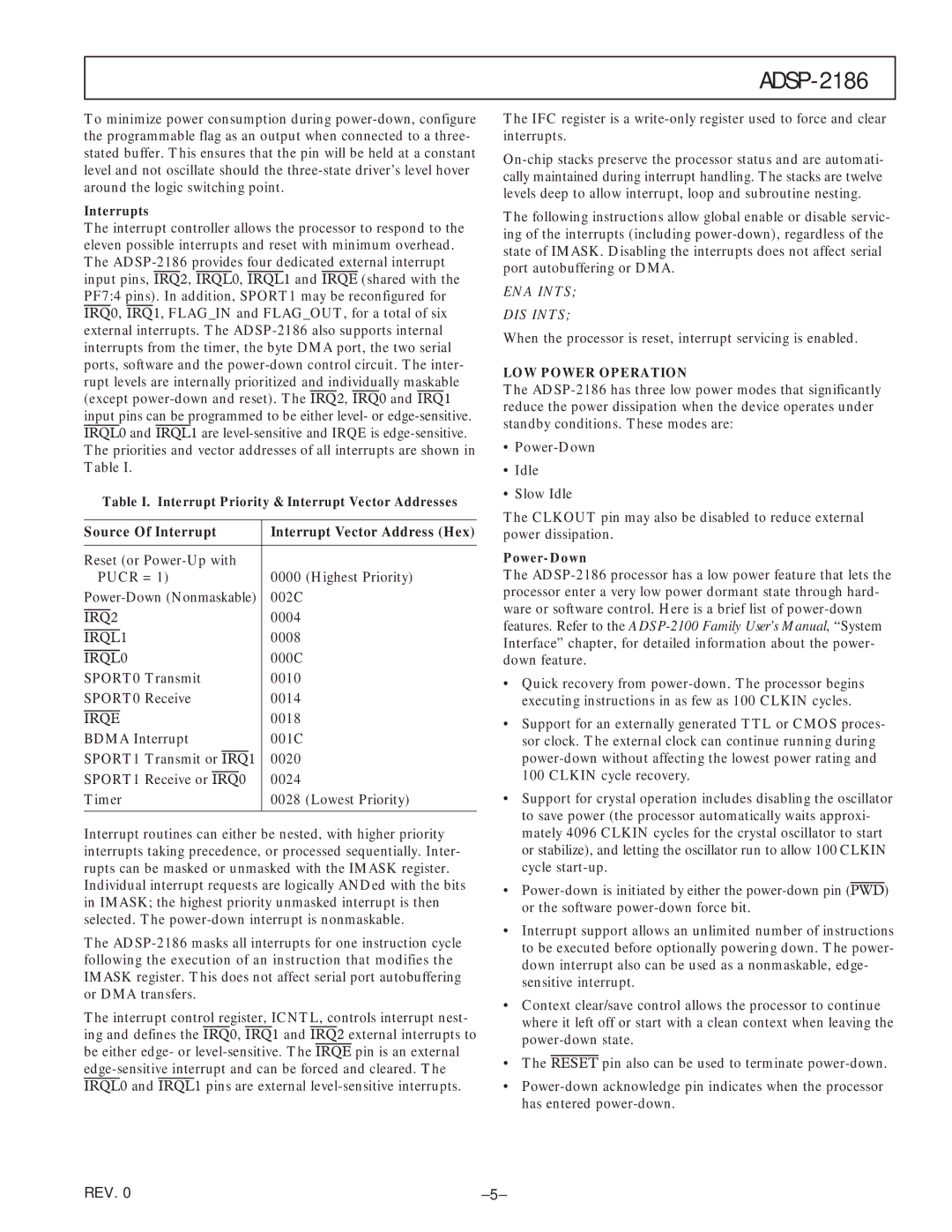

The priorities and vector addresses of all interrupts are shown in Table I.

Table I. Interrupt Priority & Interrupt Vector Addresses

Source Of Interrupt | Interrupt Vector Address (Hex) |

|

|

Reset (or |

|

PUCR = 1) | 0000 (Highest Priority) |

002C | |

IRQ2 | 0004 |

IRQL1 | 0008 |

IRQL0 | 000C |

SPORT0 Transmit | 0010 |

SPORT0 Receive | 0014 |

IRQE | 0018 |

BDMA Interrupt | 001C |

SPORT1 Transmit or IRQ1 | 0020 |

SPORT1 Receive or IRQ0 | 0024 |

Timer | 0028 (Lowest Priority) |

|

|

Interrupt routines can either be nested, with higher priority interrupts taking precedence, or processed sequentially. Inter- rupts can be masked or unmasked with the IMASK register. Individual interrupt requests are logically ANDed with the bits in IMASK; the highest priority unmasked interrupt is then selected. The

The

The interrupt control register, ICNTL, controls interrupt nest- ing and defines the IRQ0, IRQ1 and IRQ2 external interrupts to

be either edge- or

The IFC register is a

The following instructions allow global enable or disable servic- ing of the interrupts (including

ENA INTS;

DIS INTS;

When the processor is reset, interrupt servicing is enabled.

LOW POWER OPERATION

The

•

•Idle

•Slow Idle

The CLKOUT pin may also be disabled to reduce external power dissipation.

Power-Down

The

•Quick recovery from

•Support for an externally generated TTL or CMOS proces- sor clock. The external clock can continue running during

•Support for crystal operation includes disabling the oscillator to save power (the processor automatically waits approxi- mately 4096 CLKIN cycles for the crystal oscillator to start or stabilize), and letting the oscillator run to allow 100 CLKIN cycle

•

•Interrupt support allows an unlimited number of instructions to be executed before optionally powering down. The power- down interrupt also can be used as a nonmaskable, edge- sensitive interrupt.

•Context clear/save control allows the processor to continue where it left off or start with a clean context when leaving the

•The RESET pin also can be used to terminate

•

REV. 0 |