|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Parameter |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Min | Max | Unit |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

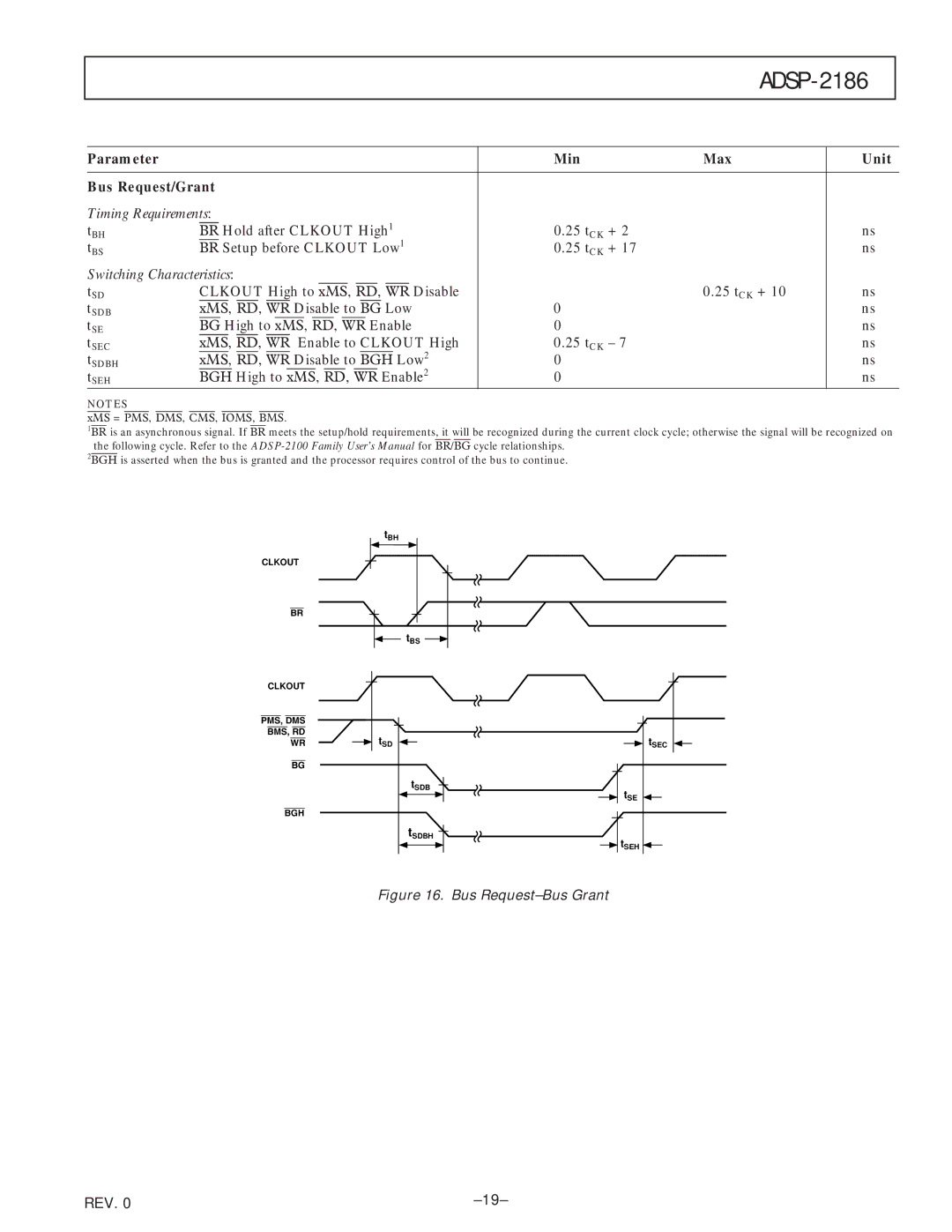

| Bus Request/Grant |

|

|

|

| ||||||||||||||||||||||||||

| Timing Requirements: |

|

|

|

| ||||||||||||||||||||||||||

| tBH | BR |

| Hold after CLKOUT High1 | 0.25 tCK + 2 |

| ns |

| |||||||||||||||||||||||

| tBS | BR Setup before CLKOUT Low1 | 0.25 tCK + 17 |

| ns |

| |||||||||||||||||||||||||

| Switching Characteristics: |

|

|

|

| ||||||||||||||||||||||||||

| tSD | CLKOUT High to | xMS | , |

| RD | , | WR | Disable |

| 0.25 tCK + 10 | ns |

| ||||||||||||||||||

| tSDB | xMS, RD, WR Disable to BG Low | 0 |

| ns |

| |||||||||||||||||||||||||

| tSE | BG | High to | xMS | , | RD | , | WR | Enable | 0 |

| ns |

| ||||||||||||||||||

| tSEC | xMS | , | RD | , | WR | Enable to CLKOUT High | 0.25 tCK – 7 |

| ns |

| ||||||||||||||||||||

| tSDBH | xMS, RD, WR Disable to BGH Low2 | 0 |

| ns |

| |||||||||||||||||||||||||

| tSEH | BGH | High to | xMS | , | RD | , | WR | Enable2 | 0 |

| ns |

| ||||||||||||||||||

NOTES

xMS = PMS, DMS, CMS, IOMS, BMS.

1BR is an asynchronous signal. If BR meets the setup/hold requirements, it will be recognized during the current clock cycle; otherwise the signal will be recognized on the following cycle. Refer to the

2BGH is asserted when the bus is granted and the processor requires control of the bus to continue.

CLKOUT

BR

CLKOUT

PMS, DMS BMS, RD WR

BG

BGH

tBH

tBS

tSD

tSDB

tSDBH

tSEC

tSE

![]() tSEH

tSEH ![]()

Figure 16. Bus Request–Bus Grant

REV. 0 |