ADSP-2186

biased rounding, result free ALU operations, I/O memory trans- fers and global interrupt masking for increased flexibility.

Fabricated in a high speed, double metal, low power, CMOS process, the

The

•Generate the next program address

•Fetch the next instruction

•Perform one or two data moves

•Update one or two data address pointers

•Perform a computational operation

This takes place while the processor continues to:

•Receive and transmit data through the two serial ports

•Receive and/or transmit data through the internal DMA port

•Receive and/or transmit data through the byte DMA port

•Decrement timer

Development System

The

C Compiler, generates |

The source code debugger allows programs to be corrected in |

The

•

•Up to 20 breakpoints

•

•Registers and memory values can be examined and altered

•PC upload and download functions

•

•Complete assembly and disassembly of instructions

•C

See Designing An

Additional Information

This data sheet provides a general overview of

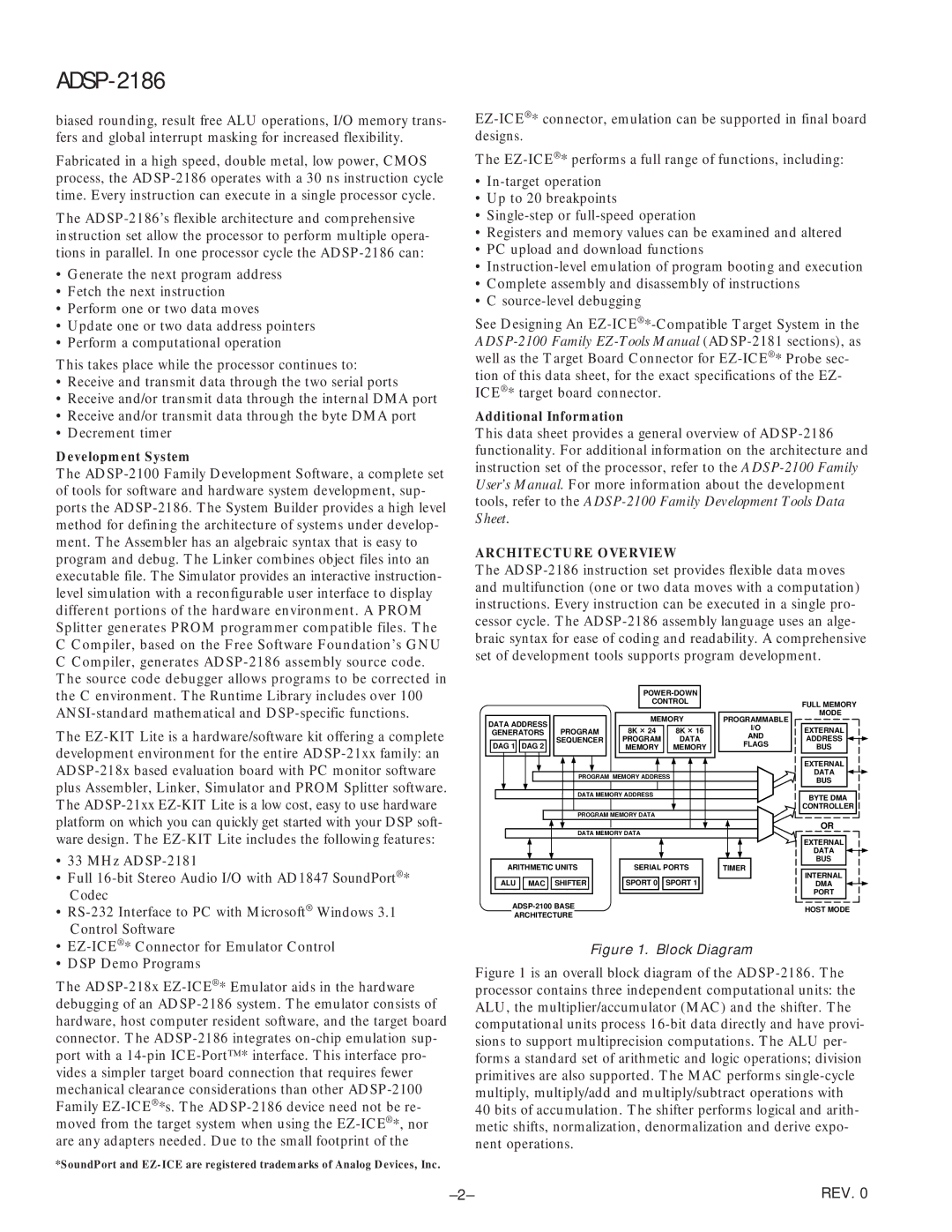

ARCHITECTURE OVERVIEW

The

the C environment. The Runtime Library includes over 100 |

|

The

• 33 MHz |

• Full |

Codec |

• |

Control Software |

® |

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

| CONTROL |

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DATA ADDRESS |

|

|

|

|

| MEMORY |

| PROGRAMMABLE | ||||||||

| GENERATORS |

| PROGRAM |

|

| 8K 24 |

| 8K 16 |

|

| I/O | |||||

|

|

|

|

|

|

| AND | |||||||||

|

|

|

|

|

| SEQUENCER |

|

| PROGRAM |

| DATA |

|

| |||

| DAG 1 |

| DAG 2 |

|

|

|

|

| MEMORY |

| MEMORY |

|

| FLAGS | ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PROGRAM MEMORY ADDRESS |

DATA MEMORY ADDRESS |

PROGRAM MEMORY DATA |

DATA MEMORY DATA

| ARITHMETIC UNITS |

|

| SERIAL PORTS |

| TIMER | ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ALU |

| MAC |

| SHIFTER |

|

|

| SPORT 0 |

| SPORT 1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ARCHITECTURE

FULL MEMORY

MODE

EXTERNAL ADDRESS ![]()

![]()

BUS

EXTERNAL DATA ![]()

![]() BUS

BUS

BYTE DMA

CONTROLLER

OR

EXTERNAL DATA ![]()

![]()

![]() BUS

BUS

INTERNAL

DMA

PORT

HOST MODE

• |

• DSP Demo Programs |

The

*SoundPort and

Figure 1. Block Diagram

Figure 1 is an overall block diagram of the ADSP-2186. The processor contains three independent computational units: the ALU, the multiplier/accumulator (MAC) and the shifter. The computational units process 16-bit data directly and have provi- sions to support multiprecision computations. The ALU per- forms a standard set of arithmetic and logic operations; division primitives are also supported. The MAC performs single-cycle multiply, multiply/add and multiply/subtract operations with

40 bits of accumulation. The shifter performs logical and arith- metic shifts, normalization, denormalization and derive expo- nent operations.

REV. 0 |