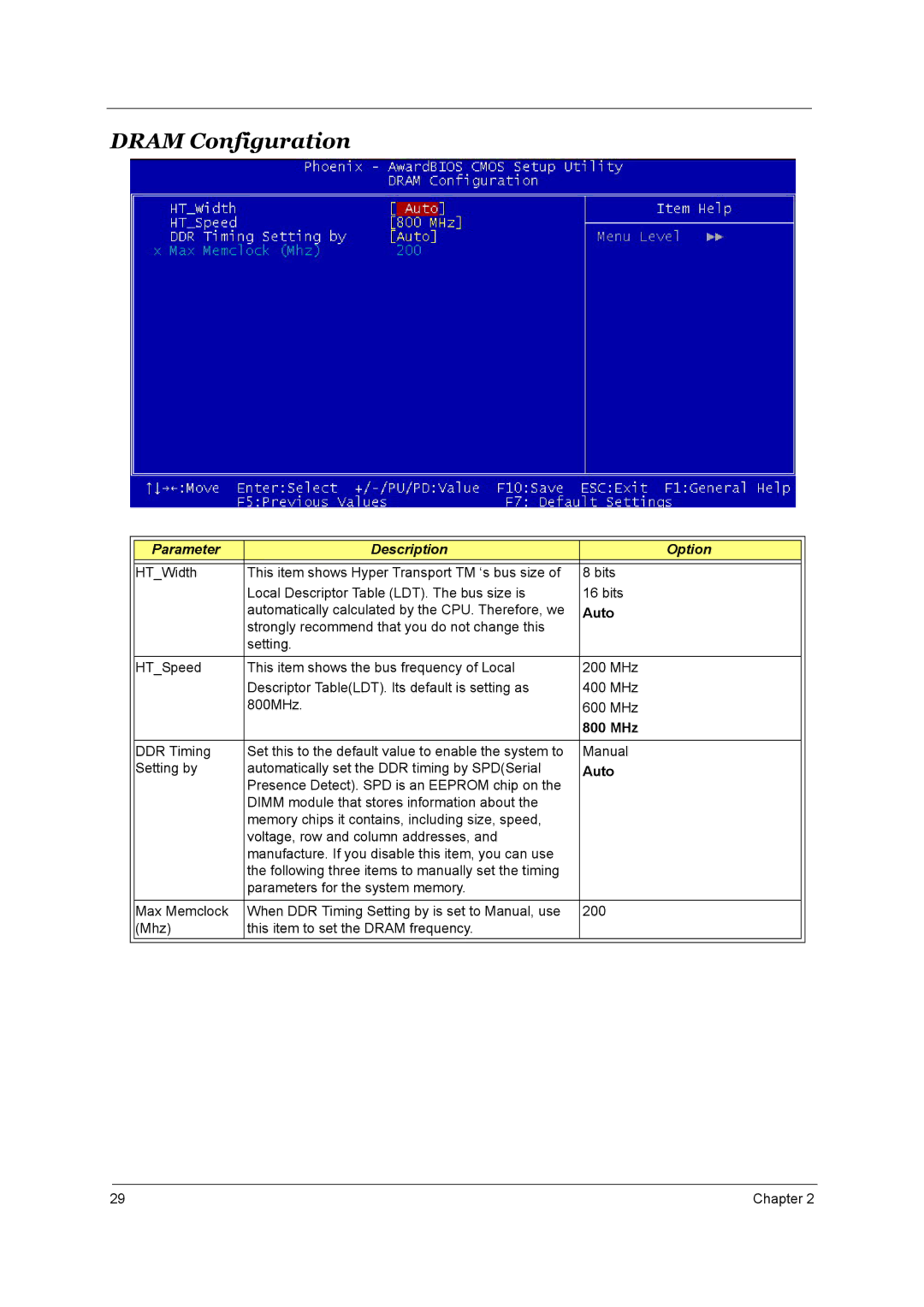

DRAM Configuration

|

|

|

|

|

| Parameter | Description | Option |

|

|

|

|

|

|

| HT_Width | This item shows Hyper Transport TM ‘s bus size of | 8 bits |

|

|

| Local Descriptor Table (LDT). The bus size is | 16 bits |

|

|

| automatically calculated by the CPU. Therefore, we | Auto |

|

|

| strongly recommend that you do not change this |

|

|

|

| setting. |

|

|

|

|

|

|

|

| HT_Speed | This item shows the bus frequency of Local | 200 MHz |

|

|

| Descriptor Table(LDT). Its default is setting as | 400 MHz |

|

|

| 800MHz. | 600 MHz |

|

|

|

| 800 MHz |

|

|

|

|

|

|

| DDR Timing | Set this to the default value to enable the system to | Manual |

|

| Setting by | automatically set the DDR timing by SPD(Serial | Auto |

|

|

| Presence Detect). SPD is an EEPROM chip on the |

|

|

|

| DIMM module that stores information about the |

|

|

|

| memory chips it contains, including size, speed, |

|

|

|

| voltage, row and column addresses, and |

|

|

|

| manufacture. If you disable this item, you can use |

|

|

|

| the following three items to manually set the timing |

|

|

|

| parameters for the system memory. |

|

|

|

|

|

|

|

| Max Memclock | When DDR Timing Setting by is set to Manual, use | 200 |

|

| (Mhz) | this item to set the DRAM frequency. |

|

|

|

|

|

|

|

29 | Chapter 2 |