|

|

|

|

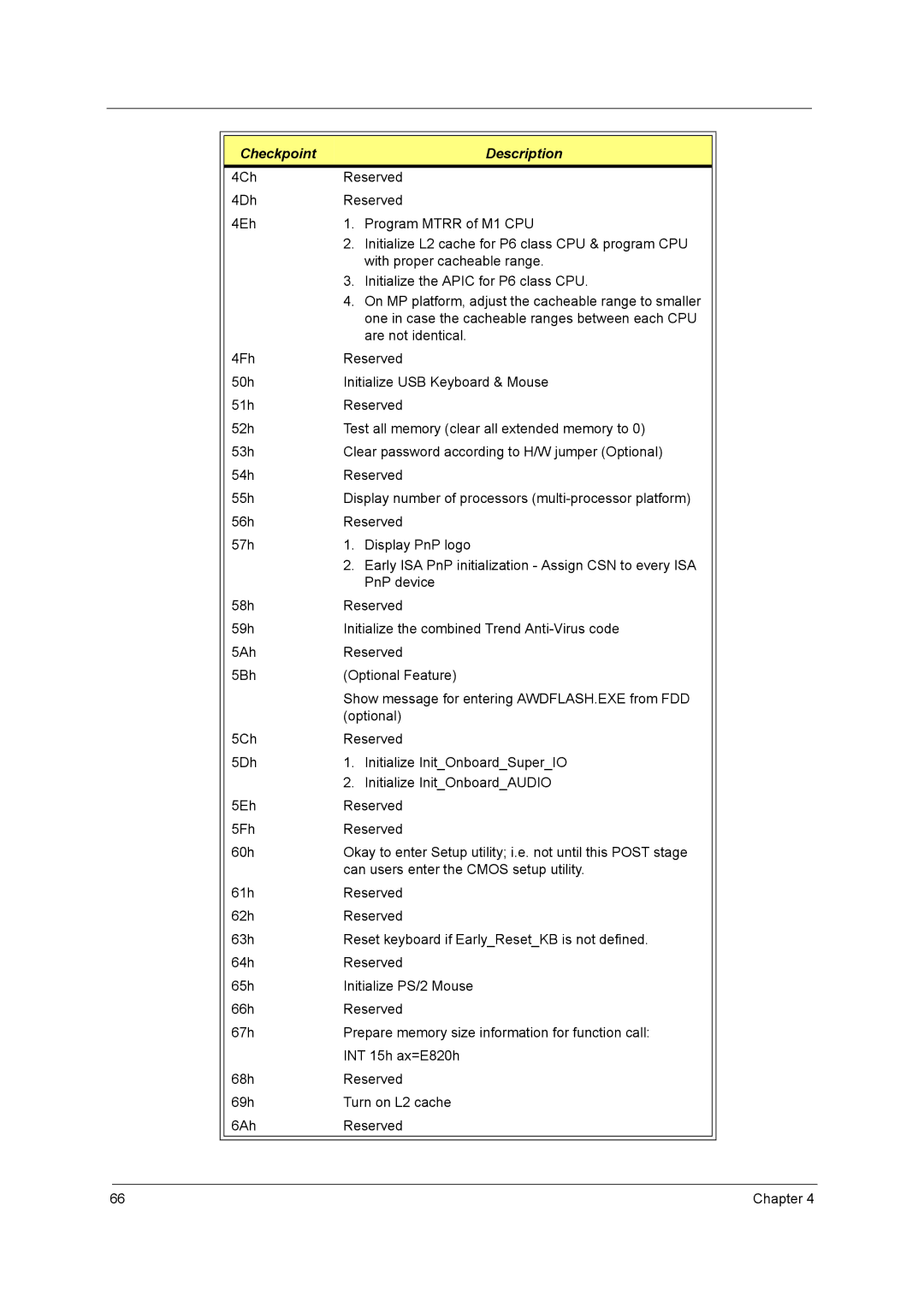

| Checkpoint | Description |

|

| 4Ch | Reserved |

|

| 4Dh | Reserved |

|

| 4Eh | 1. Program MTRR of M1 CPU |

|

|

| 2. Initialize L2 cache for P6 class CPU & program CPU |

|

|

| with proper cacheable range. |

|

|

| 3. Initialize the APIC for P6 class CPU. |

|

|

| 4. On MP platform, adjust the cacheable range to smaller |

|

|

| one in case the cacheable ranges between each CPU |

|

|

| are not identical. |

|

| 4Fh | Reserved |

|

| 50h | Initialize USB Keyboard & Mouse |

|

| 51h | Reserved |

|

| 52h | Test all memory (clear all extended memory to 0) |

|

| 53h | Clear password according to H/W jumper (Optional) |

|

| 54h | Reserved |

|

| 55h | Display number of processors |

|

| 56h | Reserved |

|

| 57h | 1. Display PnP logo |

|

|

| 2. Early ISA PnP initialization - Assign CSN to every ISA |

|

|

| PnP device |

|

| 58h | Reserved |

|

| 59h | Initialize the combined Trend |

|

| 5Ah | Reserved |

|

| 5Bh | (Optional Feature) |

|

|

| Show message for entering AWDFLASH.EXE from FDD |

|

|

| (optional) |

|

| 5Ch | Reserved |

|

| 5Dh | 1. Initialize Init_Onboard_Super_IO |

|

|

| 2. Initialize Init_Onboard_AUDIO |

|

| 5Eh | Reserved |

|

| 5Fh | Reserved |

|

| 60h | Okay to enter Setup utility; i.e. not until this POST stage |

|

|

| can users enter the CMOS setup utility. |

|

| 61h | Reserved |

|

| 62h | Reserved |

|

| 63h | Reset keyboard if Early_Reset_KB is not defined. |

|

| 64h | Reserved |

|

| 65h | Initialize PS/2 Mouse |

|

| 66h | Reserved |

|

| 67h | Prepare memory size information for function call: |

|

|

| INT 15h ax=E820h |

|

| 68h | Reserved |

|

| 69h | Turn on L2 cache |

|

| 6Ah | Reserved |

|

|

|

|

|

66 | Chapter 4 |