P M C / P C I I N T E R F A C E

PCI Identification Values

. . . . .

.P.C.I. .I D. .E.N. .T.I .F.I C. .A. T. I.O. .N. .V. A. .L.U. E. .S. . . . . . . . . . . . . . . . . . . . . . .

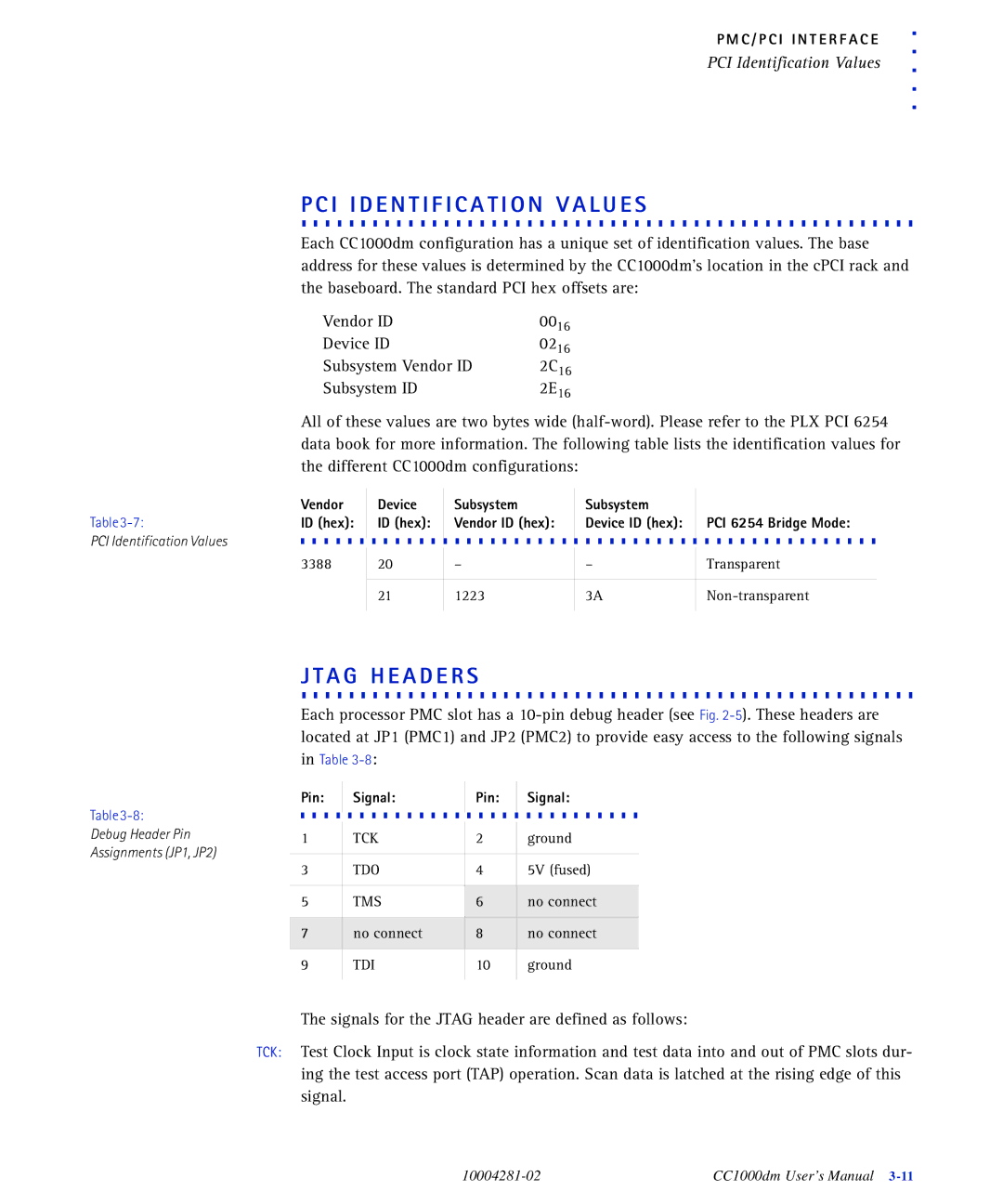

Each CC1000dm configuration has a unique set of identification values. The base address for these values is determined by the CC1000dm’s location in the cPCI rack and the baseboard. The standard PCI hex offsets are:

Vendor ID | 0016 |

Device ID | 0216 |

Subsystem Vendor ID | 2C16 |

Subsystem ID | 2E16 |

All of these values are two bytes wide

| Vendor | Device | Subsystem | |

Table | ID (hex): | ID (hex): | Vendor ID (hex): | |

PCI Identification Values |

|

|

| |

3388 | 20 | – | ||

|

Subsystem Device ID (hex):

–

PCI 6254 Bridge Mode:

Transparent

21

1223

3A

Table

Debug Header Pin Assignments (JP1, JP2)

.J .T.A.G. . H. .E.A. D. .E.R. S. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Each processor PMC slot has a

Pin: |

| Signal: |

| Pin: |

| Signal: |

1 |

| TCK |

| 2 |

| ground |

|

|

| ||||

|

|

| ||||

|

|

|

|

|

|

|

3 |

| TDO |

| 4 |

| 5V (fused) |

|

|

|

|

|

|

|

5 |

| TMS |

| 6 |

| no connect |

|

|

|

|

|

|

|

7 |

| no connect |

| 8 |

| no connect |

|

|

|

|

|

|

|

9 |

| TDI |

| 10 |

| ground |

|

|

|

|

|

|

|

The signals for the JTAG header are defined as follows:

TCK: Test Clock Input is clock state information and test data into and out of PMC slots dur- ing the test access port (TAP) operation. Scan data is latched at the rising edge of this signal.

CC1000dm User’s Manual |