P M C / P C I I N T E R F A C E | . | |

. | ||

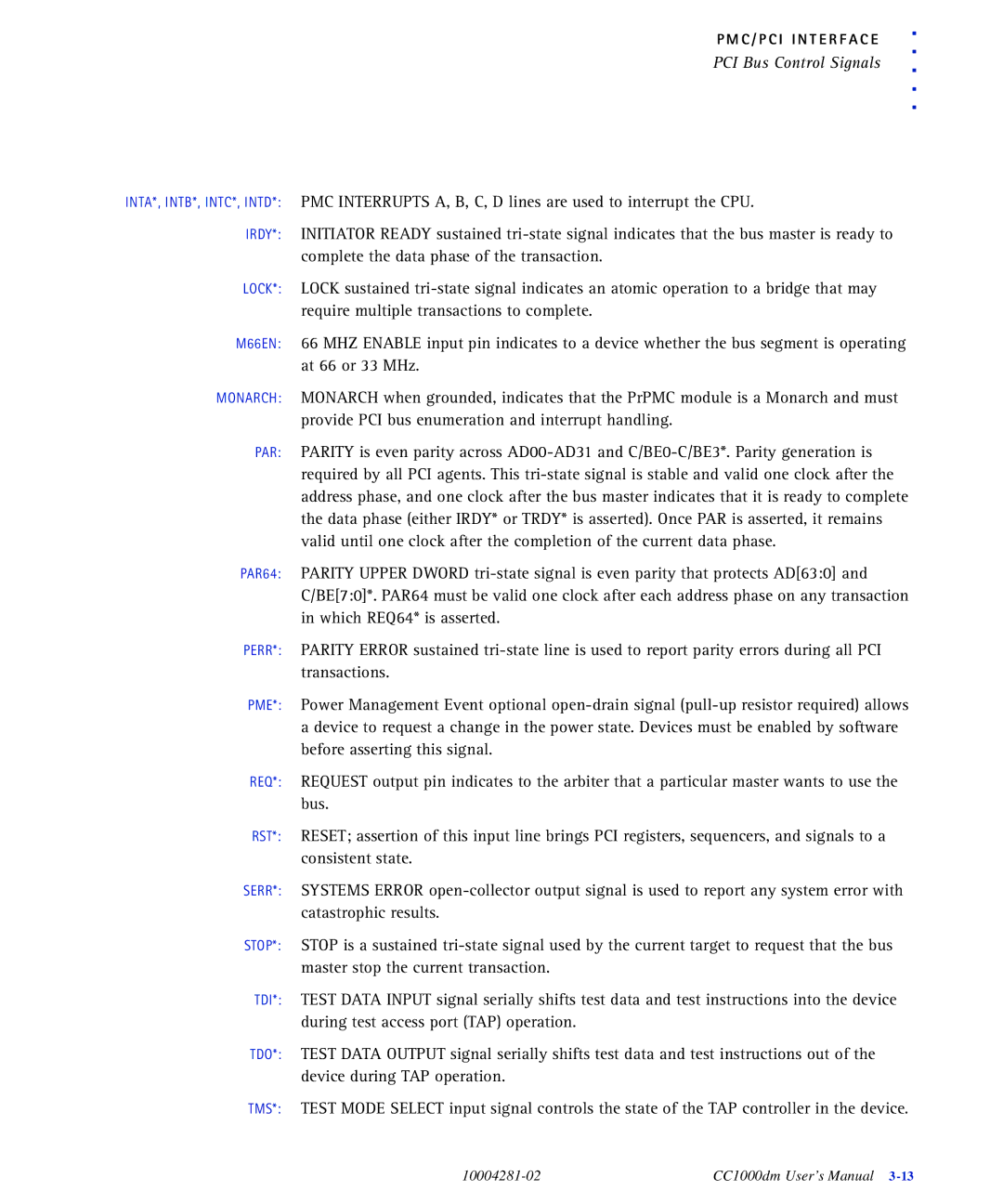

PCI Bus Control Signals | ||

. | ||

| ||

| . . |

INTA*, INTB*, INTC*, INTD*: | PMC INTERRUPTS A, B, C, D lines are used to interrupt the CPU. |

IRDY*: | INITIATOR READY sustained |

| complete the data phase of the transaction. |

LOCK*: | LOCK sustained |

| require multiple transactions to complete. |

M66EN: | 66 MHZ ENABLE input pin indicates to a device whether the bus segment is operating |

| at 66 or 33 MHz. |

MONARCH: | MONARCH when grounded, indicates that the PrPMC module is a Monarch and must |

| provide PCI bus enumeration and interrupt handling. |

PAR: | PARITY is even parity across |

| required by all PCI agents. This |

| address phase, and one clock after the bus master indicates that it is ready to complete |

| the data phase (either IRDY* or TRDY* is asserted). Once PAR is asserted, it remains |

| valid until one clock after the completion of the current data phase. |

PAR64: | PARITY UPPER DWORD |

| C/BE[7:0]*. PAR64 must be valid one clock after each address phase on any transaction |

| in which REQ64* is asserted. |

PERR*: | PARITY ERROR sustained |

| transactions. |

PME*: | Power Management Event optional |

| a device to request a change in the power state. Devices must be enabled by software |

| before asserting this signal. |

REQ*: | REQUEST output pin indicates to the arbiter that a particular master wants to use the |

| bus. |

RST*: | RESET; assertion of this input line brings PCI registers, sequencers, and signals to a |

| consistent state. |

SERR*: | SYSTEMS ERROR |

| catastrophic results. |

STOP*: | STOP is a sustained |

| master stop the current transaction. |

TDI*: | TEST DATA INPUT signal serially shifts test data and test instructions into the device |

| during test access port (TAP) operation. |

TDO*: | TEST DATA OUTPUT signal serially shifts test data and test instructions out of the |

| device during TAP operation. |

TMS*: | TEST MODE SELECT input signal controls the state of the TAP controller in the device. |

CC1000dm User’s Manual |