TABLES

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ..

. . .

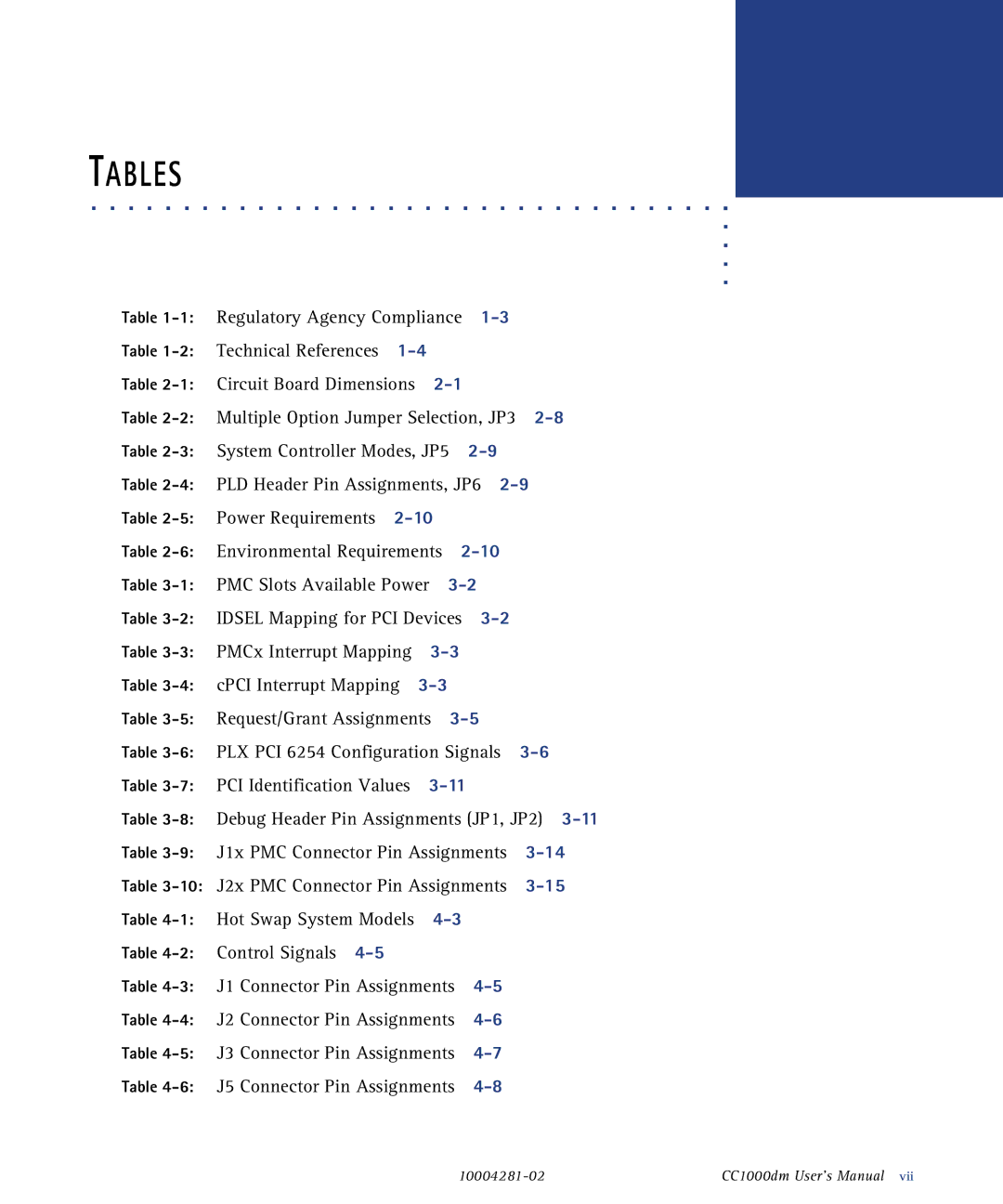

Table | Regulatory Agency Compliance |

| ||||

Table | Technical References |

|

|

|

| |

Table | Circuit Board Dimensions |

|

| |||

Table | Multiple Option Jumper Selection, JP3 | |||||

Table | System Controller Modes, JP5 |

| ||||

Table | PLD Header Pin Assignments, JP6 | |||||

Table | Power Requirements |

|

|

| ||

Table | Environmental Requirements |

| ||||

Table | PMC Slots Available Power |

|

| |||

Table | IDSEL Mapping for PCI Devices |

| ||||

Table | PMCx Interrupt Mapping |

|

| |||

Table | cPCI Interrupt Mapping |

|

|

| ||

Table | Request/Grant Assignments |

| ||||

Table | PLX PCI 6254 Configuration Signals | |||||

Table | PCI Identification Values |

|

| |||

Table | Debug Header Pin Assignments (JP1, JP2) | |||||

Table | J1x PMC Connector Pin Assignments | |||||

Table | J2x PMC Connector Pin Assignments | |||||

Table | Hot Swap System Models |

|

| |||

Table | Control Signals |

|

|

|

|

|

Table | J1 Connector Pin Assignments |

| ||||

Table | J2 Connector Pin Assignments |

| ||||

Table | J3 Connector Pin Assignments |

| ||||

Table | J5 Connector Pin Assignments |

| ||||

CC1000dm User’s Manual vii |