3

Table

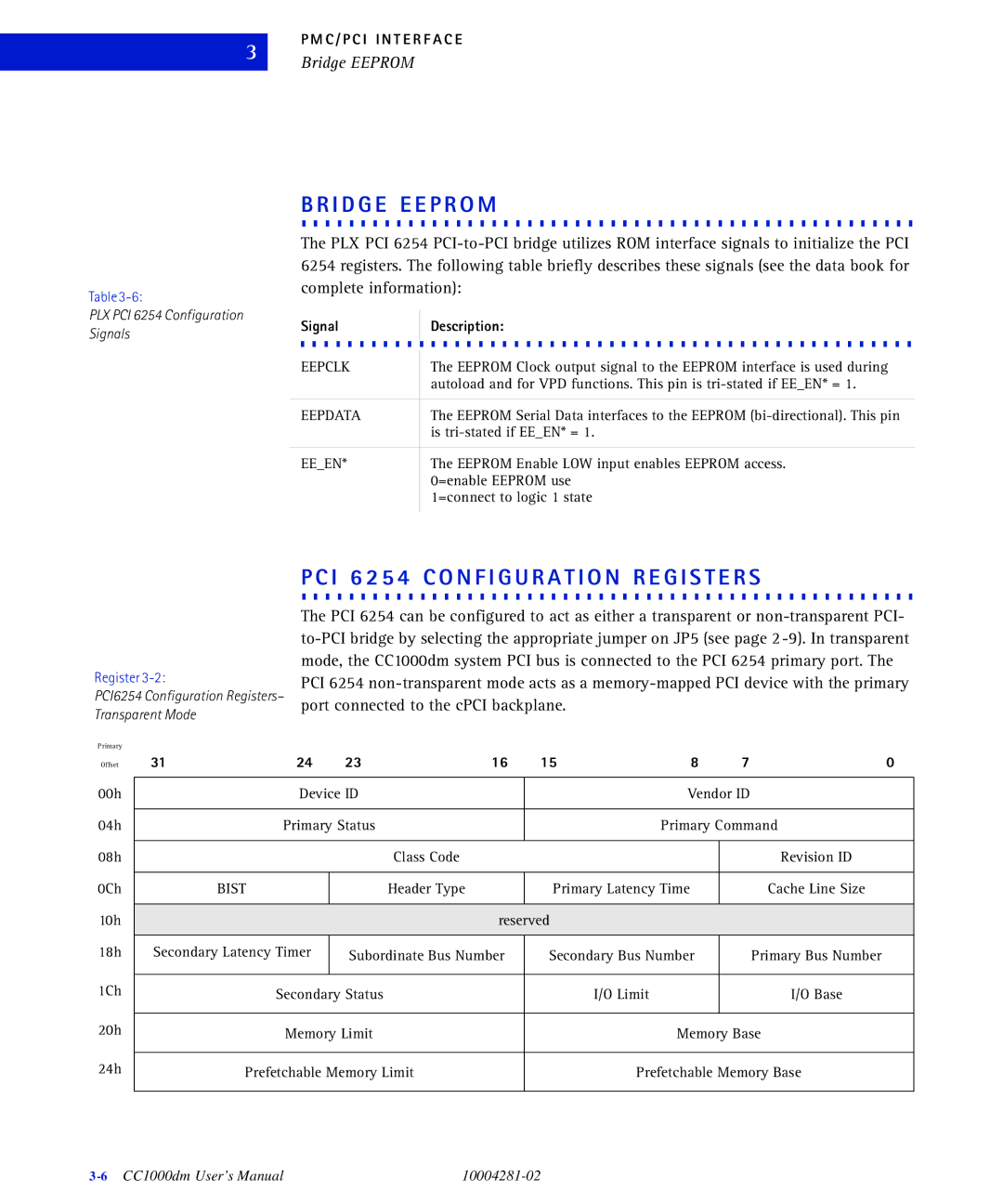

PLX PCI 6254 Configuration Signals

P M C / P C I I N T E R F A C E

Bridge EEPROM

.B.R.I.D. G. .E. .E.E. P. .R.O. M. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

The PLX PCI 6254

Signal | Description: |

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

EEPCLK | The EEPROM Clock output signal to the EEPROM interface is used during |

| autoload and for VPD functions. This pin is |

|

|

EEPDATA | The EEPROM Serial Data interfaces to the EEPROM |

| is |

|

|

EE_EN* | The EEPROM Enable LOW input enables EEPROM access. |

| 0=enable EEPROM use |

| 1=connect to logic 1 state |

|

|

Register

PCI6254 Configuration Registers– Transparent Mode

.P.C.I. .6.2. 5. .4. .C.O. .N.F. I.G. .U.R. A. .T.I .O.N. . R. .E.G. I.S. T. .E.R.S. . . . . . . . . . . . . .

The PCI 6254 can be configured to act as either a transparent or

Primary |

|

|

|

|

|

|

|

|

Offset | 31 | 24 | 23 | 16 | 15 | 8 | 7 | 0 |

|

|

|

|

|

|

|

|

|

00h |

| Device ID |

|

| Vendor ID |

| ||

|

|

|

|

|

| |||

04h |

| Primary Status |

|

| Primary Command | |||

|

|

|

|

|

|

|

|

|

08h |

|

| Class Code |

|

|

|

| Revision ID |

|

|

|

|

|

|

|

| |

0Ch |

| BIST | Header Type |

| Primary Latency Time |

| Cache Line Size | |

10h |

|

|

|

|

|

|

|

|

|

|

| reserved |

|

|

| ||

18h | Secondary Latency Timer | Subordinate Bus Number | Secondary Bus Number |

| Primary Bus Number | |||

1Ch |

|

|

|

|

|

|

|

|

| Secondary Status |

|

| I/O Limit |

| I/O Base | ||

20h |

|

|

|

|

|

| ||

| Memory Limit |

|

| Memory Base | ||||

24h |

|

|

|

|

| |||

| Prefetchable Memory Limit |

|

| Prefetchable Memory Base | ||||

|

|

|

|

|

|

|

|

|

|