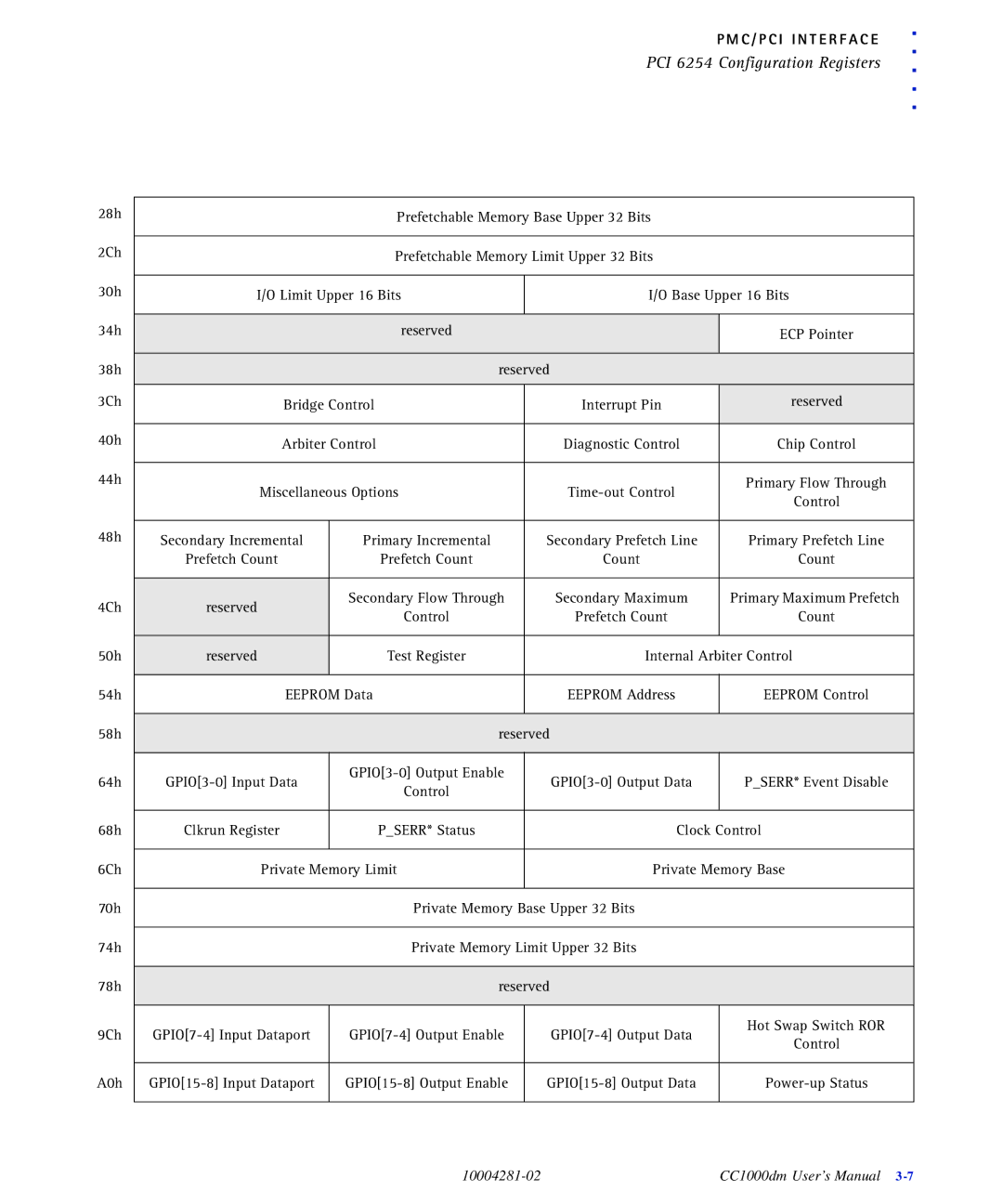

28h

2Ch

30h

34h

38h

3Ch

40h

44h

48h

4Ch

50h

54h

58h

64h

68h

6Ch

70h

74h

78h

9Ch

A0h

P M C / P C I I N T E R F A C E | . | |

. | ||

PCI 6254 Configuration Registers | ||

. | ||

| ||

| . . |

Prefetchable Memory Base Upper 32 Bits

Prefetchable Memory Limit Upper 32 Bits

I/O Limit Upper 16 Bits | I/O Base Upper 16 Bits | |||

|

|

|

| |

| reserved |

| ECP Pointer | |

|

|

|

| |

| reserved |

| ||

Bridge Control | Interrupt Pin | reserved | ||

|

|

| ||

Arbiter Control | Diagnostic Control | Chip Control | ||

|

|

|

| |

Miscellaneous Options | Primary Flow Through | |||

Control | ||||

|

|

| ||

|

|

|

| |

Secondary Incremental | Primary Incremental | Secondary Prefetch Line | Primary Prefetch Line | |

Prefetch Count | Prefetch Count | Count | Count | |

|

|

|

| |

reserved | Secondary Flow Through | Secondary Maximum | Primary Maximum Prefetch | |

Control | Prefetch Count | Count | ||

| ||||

|

|

|

| |

reserved | Test Register | Internal Arbiter Control | ||

|

|

|

| |

EEPROM Data | EEPROM Address | EEPROM Control | ||

|

|

|

| |

| reserved |

| ||

|

|

|

| |

P_SERR* Event Disable | ||||

Control | ||||

|

|

| ||

|

|

|

| |

Clkrun Register | P_SERR* Status | Clock Control | ||

|

|

|

| |

Private Memory Limit | Private Memory Base | |||

|

|

|

| |

Private Memory Base Upper 32 Bits

Private Memory Limit Upper 32 Bits

reserved

Hot Swap Switch ROR | ||||

Control | ||||

|

|

| ||

|

|

|

| |

|

|

|

|

CC1000dm User’s Manual |