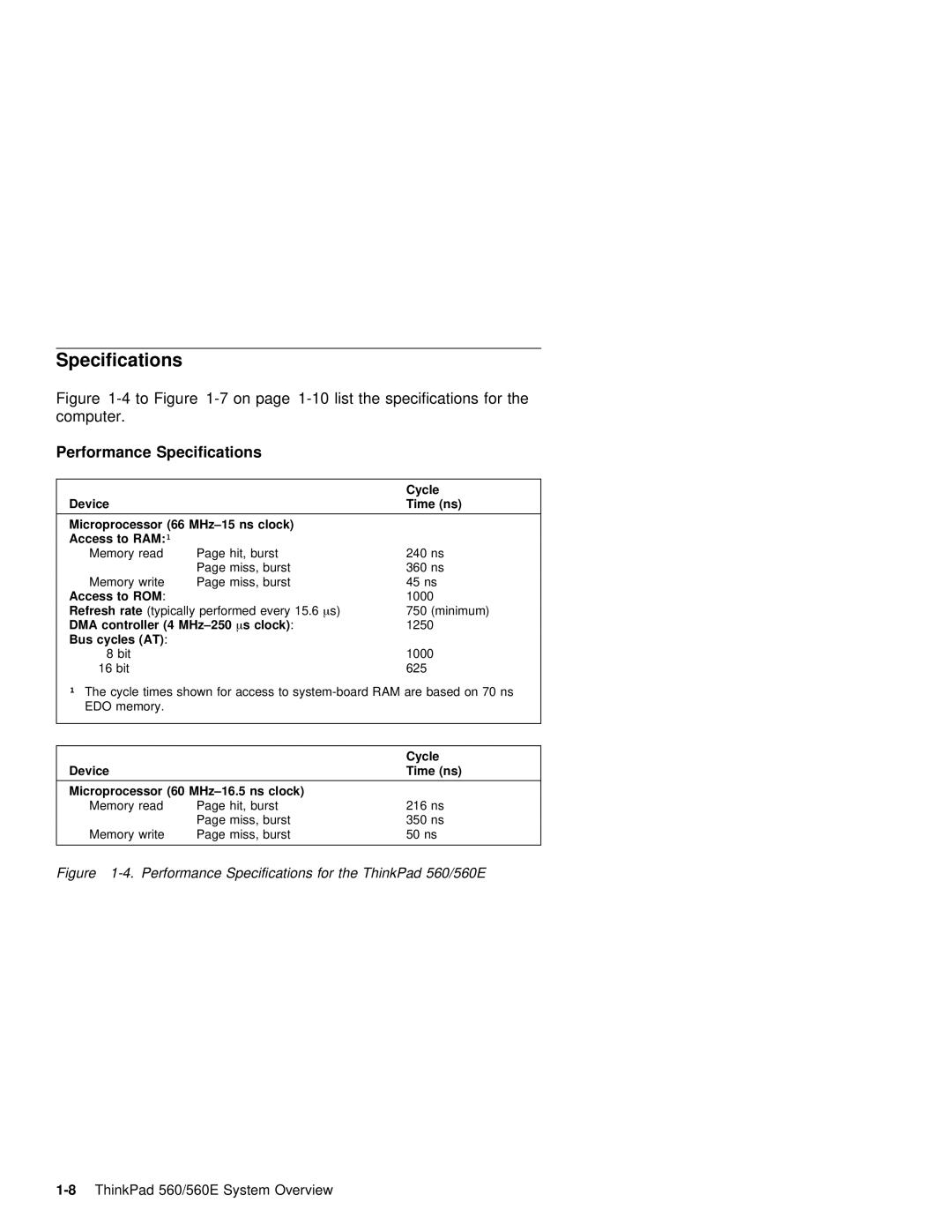

Specifications

Figure | to Figure |

| on | page | list the | specifications | for the | |||||||||

computer. |

|

|

|

|

|

|

|

|

|

|

|

|

| |||

Performance | Specifications |

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

| Cycle |

|

|

|

| |

Device |

|

|

|

|

|

|

|

|

| Time | (ns) |

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

Microprocessor | (66 | ns | clock) |

|

|

|

|

|

|

|

|

| ||||

Access | to | RAM: | ñ |

|

|

|

|

|

|

|

|

|

|

|

| |

| Memory | read | Page |

| hit, |

| burst | 240 | ns |

|

|

| ||||

|

|

|

| Page | miss, | burst |

| 360 | ns |

|

|

| ||||

| Memory | write | Page | miss, | burst | 45 |

| ns |

|

|

| |||||

Access | to | ROM | : |

|

|

|

|

|

| 1000 |

|

|

|

| ||

Refresh | rate | (typically | performed | µeverys) | 15.6 750 |

| (minimum) |

|

|

| ||||||

DMA | controller | (4 | µs | clock) | : |

| 1250 |

|

|

| ||||||

Bus | cycles | (AT) : |

|

|

|

|

|

|

|

|

|

|

|

| ||

|

| 8 bit |

|

|

|

|

|

|

| 1000 |

|

|

|

| ||

|

| 16 bit |

|

|

|

|

|

|

| 625 |

|

|

|

| ||

ñ | The | cycle | times | shown | for | access to | are | based on 70 | ns | |||||||

| EDO | memory. |

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

| Cycle |

|

|

|

| |

Device |

|

|

|

|

|

|

|

|

| Time | (ns) |

|

|

| ||

|

|

|

|

|

|

|

|

|

| |||||||

Microprocessor (60 |

|

|

|

|

|

|

|

|

| |||||||

| Memory | read | Page |

| hit, |

| burst | 216 | ns |

|

|

| ||||

|

|

|

| Page | miss, | burst |

| 350 | ns |

|

|

| ||||

| Memory | write | Page | miss, | burst | 50 | ns |

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|