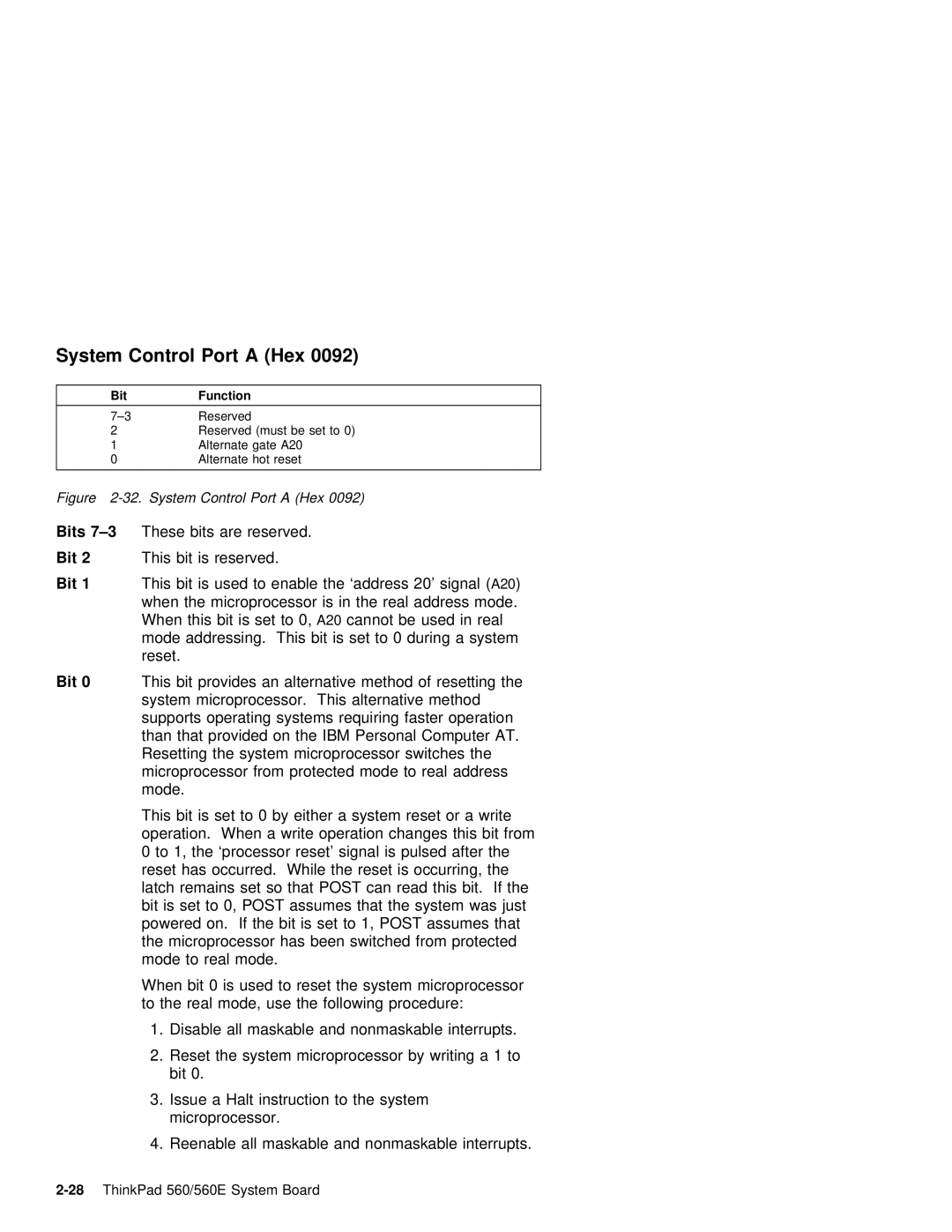

System Control | Port A (Hex | 0092) | |

|

|

|

|

Bit | Function |

|

|

|

|

|

|

Reserved |

|

| |

2 | Reserved (must be set to 0) | ||

1 | Alternate | gate | A20 |

0 | Alternate | hot | reset |

|

|

|

|

Figure | (Hex | 0092) |

|

|

|

|

|

| ||||||

Bits | These | bits | are | reserved. |

|

|

|

|

|

|

| |||

Bit | 2 | This | bit | is | reserved. |

|

|

|

|

|

|

| ||

Bit | 1 | This | bit | is used to enable the ‘addressA20 ) | 20’ signal ( | |||||||||

|

| when | the | microprocessor is | in | the | real | address | mode. | |||||

|

| When | this | bit | is A20set cannotto0, be used | in | real |

| ||||||

|

| mode | addressing. This | bit | is | set | to | 0 | during a | system | ||||

reset.

Bit 0 This bit provides an alternative method of resetting the system microprocessor. This alternative method

supports operating systems requiring faster operation than that provided on the IBM Personal Computer AT. Resetting the system microprocessor switches the microprocessor from protected mode to real address mode.

This | bit is set to 0 by either a system reset or a write | |||||||||||||||||

operation. When | a | write | operation | changes |

| this | bit | from |

| |||||||||

0 | to | 1, the ‘processor reset’ signal is | pulsed | after | the | |||||||||||||

reset has occurred. While the reset is |

| occurring, | the |

| ||||||||||||||

latch | remains | set | so | that POST | can | read | this | bit. | If | the | ||||||||

bit | is set to 0, POST assumes that the | system | was | just | ||||||||||||||

powered on. If the bit is | set | to | 1, | POST | assumes | that | ||||||||||||

the | microprocessor | has | been | switched from | protected |

| ||||||||||||

mode | to | real | mode. |

|

|

|

|

|

|

|

|

|

|

|

| |||

When | bit | 0 | is | used | to | reset | the | system | microprocessor | |||||||||

to | the real | mode, | use | the | following | procedure: |

|

|

| |||||||||

1. Disable all maskable and nonmaskable interrupts.

2. Reset the system microprocessor by writing a 1 to bit 0.

3.Issue a Halt instruction to the system microprocessor.

4.Reenable all maskable and nonmaskable interrupts.