MPCMM0002

4.6FPGA

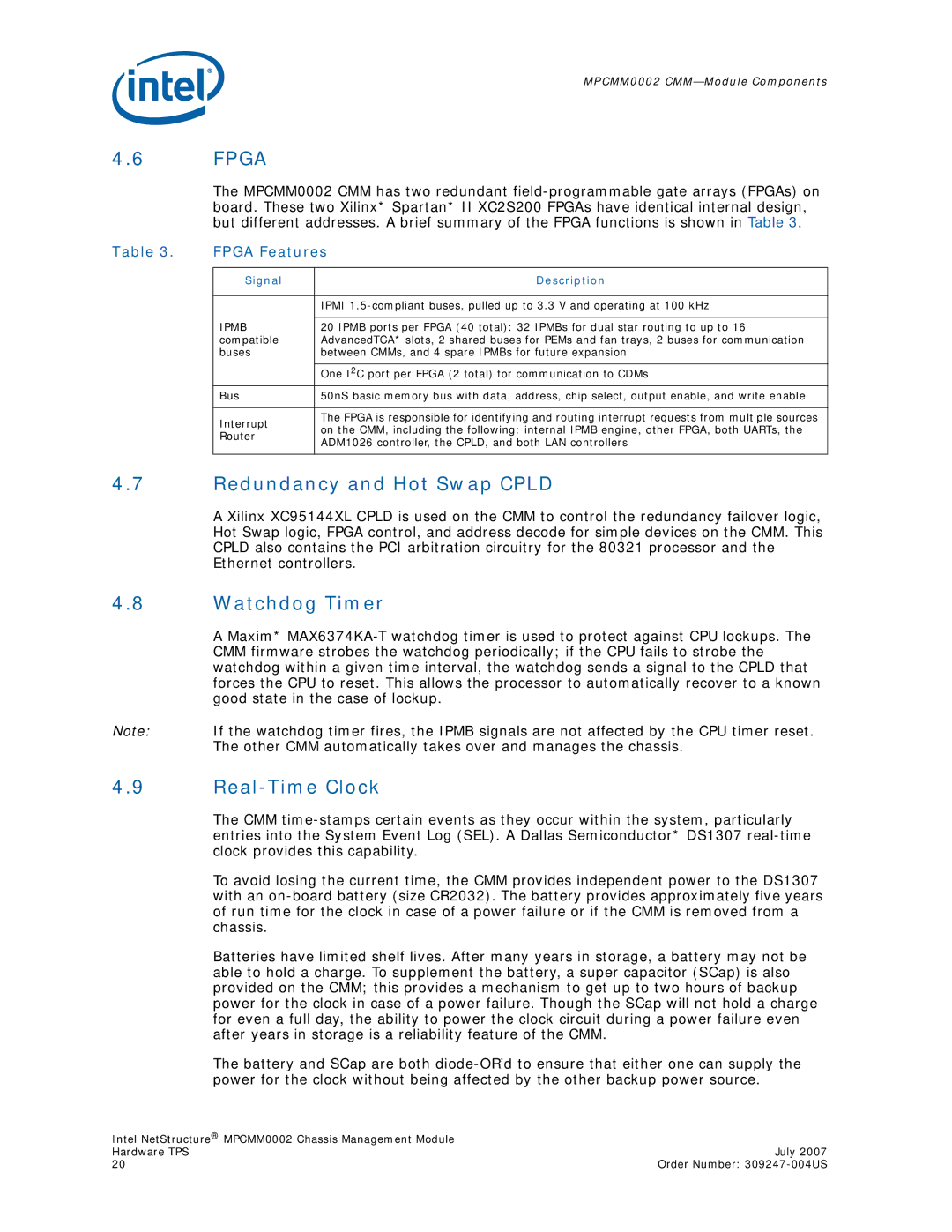

The MPCMM0002 CMM has two redundant

Table 3. | FPGA Features | |

|

|

|

| Signal | Description |

|

|

|

|

| IPMI |

|

|

|

| IPMB | 20 IPMB ports per FPGA (40 total): 32 IPMBs for dual star routing to up to 16 |

| compatible | AdvancedTCA* slots, 2 shared buses for PEMs and fan trays, 2 buses for communication |

| buses | between CMMs, and 4 spare IPMBs for future expansion |

|

|

|

|

| One I2C port per FPGA (2 total) for communication to CDMs |

| Bus | 50nS basic memory bus with data, address, chip select, output enable, and write enable |

|

|

|

| Interrupt | The FPGA is responsible for identifying and routing interrupt requests from multiple sources |

| on the CMM, including the following: internal IPMB engine, other FPGA, both UARTs, the | |

| Router | |

| ADM1026 controller, the CPLD, and both LAN controllers | |

|

| |

|

|

|

4.7Redundancy and Hot Swap CPLD

A Xilinx XC95144XL CPLD is used on the CMM to control the redundancy failover logic, Hot Swap logic, FPGA control, and address decode for simple devices on the CMM. This CPLD also contains the PCI arbitration circuitry for the 80321 processor and the Ethernet controllers.

4.8Watchdog Timer

A Maxim*

Note: If the watchdog timer fires, the IPMB signals are not affected by the CPU timer reset. The other CMM automatically takes over and manages the chassis.

4.9Real-Time Clock

The CMM

To avoid losing the current time, the CMM provides independent power to the DS1307 with an

Batteries have limited shelf lives. After many years in storage, a battery may not be able to hold a charge. To supplement the battery, a super capacitor (SCap) is also provided on the CMM; this provides a mechanism to get up to two hours of backup power for the clock in case of a power failure. Though the SCap will not hold a charge for even a full day, the ability to power the clock circuit during a power failure even after years in storage is a reliability feature of the CMM.

The battery and SCap are both

Intel NetStructure® MPCMM0002 Chassis Management Module |

|

Hardware TPS | July 2007 |

20 | Order Number: |