MPCMM0002

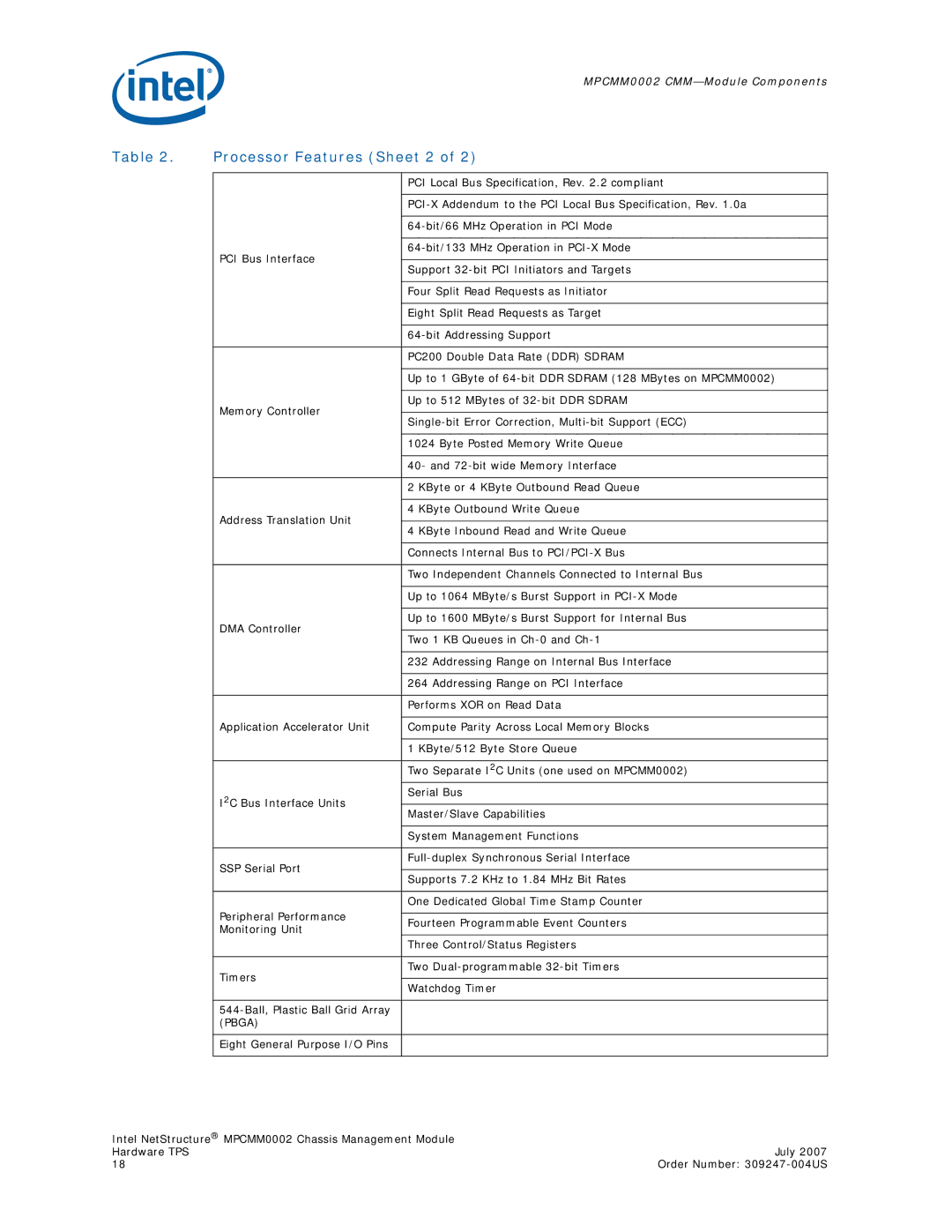

Table 2. | Processor Features (Sheet 2 of 2) | |

|

|

|

|

| PCI Local Bus Specification, Rev. 2.2 compliant |

|

|

|

|

| |

|

|

|

|

| |

|

|

|

| PCI Bus Interface | |

|

| |

| Support | |

|

| |

|

|

|

|

| Four Split Read Requests as Initiator |

|

|

|

|

| Eight Split Read Requests as Target |

|

|

|

|

| |

|

|

|

|

| PC200 Double Data Rate (DDR) SDRAM |

|

|

|

|

| Up to 1 GByte of |

|

|

|

| Memory Controller | Up to 512 MBytes of |

|

| |

| ||

|

| |

|

|

|

|

| 1024 Byte Posted Memory Write Queue |

|

|

|

|

| 40- and |

|

|

|

|

| 2 KByte or 4 KByte Outbound Read Queue |

|

|

|

| Address Translation Unit | 4 KByte Outbound Write Queue |

|

| |

| 4 KByte Inbound Read and Write Queue | |

|

| |

|

|

|

|

| Connects Internal Bus to |

|

|

|

|

| Two Independent Channels Connected to Internal Bus |

|

|

|

|

| Up to 1064 MByte/s Burst Support in |

|

|

|

| DMA Controller | Up to 1600 MByte/s Burst Support for Internal Bus |

|

| |

| Two 1 KB Queues in | |

|

| |

|

|

|

|

| 232 Addressing Range on Internal Bus Interface |

|

|

|

|

| 264 Addressing Range on PCI Interface |

|

|

|

|

| Performs XOR on Read Data |

|

|

|

| Application Accelerator Unit | Compute Parity Across Local Memory Blocks |

|

|

|

|

| 1 KByte/512 Byte Store Queue |

|

|

|

|

| Two Separate I2C Units (one used on MPCMM0002) |

| I2C Bus Interface Units | Serial Bus |

|

| |

| Master/Slave Capabilities | |

|

| |

|

|

|

|

| System Management Functions |

|

|

|

| SSP Serial Port | |

|

| |

| Supports 7.2 KHz to 1.84 MHz Bit Rates | |

|

| |

|

|

|

|

| One Dedicated Global Time Stamp Counter |

| Peripheral Performance |

|

| Fourteen Programmable Event Counters | |

| Monitoring Unit | |

|

| |

|

| Three Control/Status Registers |

|

|

|

| Timers | Two |

|

| |

| Watchdog Timer | |

|

| |

|

|

|

|

| |

| (PBGA) |

|

|

|

|

| Eight General Purpose I/O Pins |

|

|

|

|

Intel NetStructure® MPCMM0002 Chassis Management Module |

|

Hardware TPS | July 2007 |

18 | Order Number: |