MPCMM0002

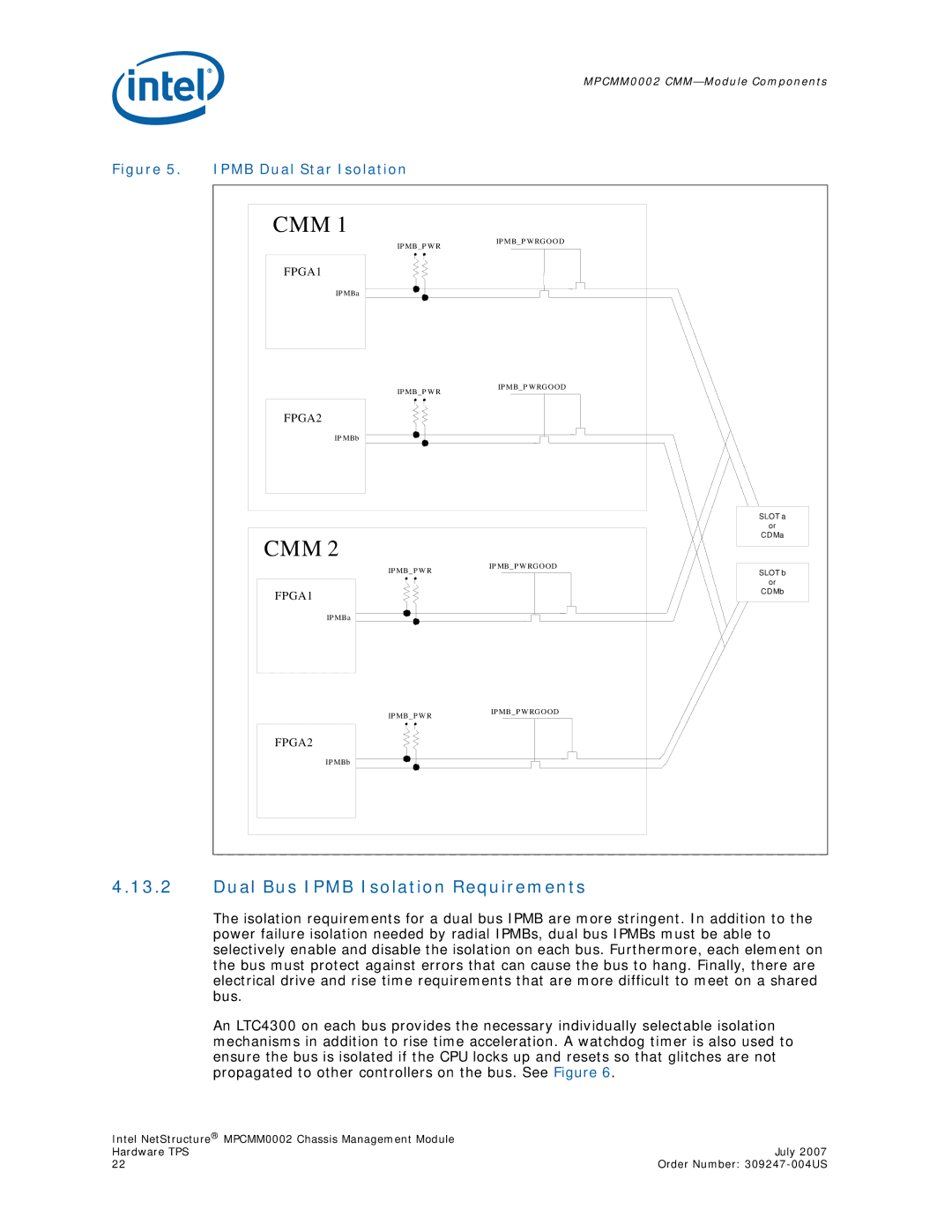

Figure 5. IPMB Dual Star Isolation

CMM 1 | IP MB_P W RG OO D | |

IP MB_P W R | ||

| ||

FPGA1 |

| |

IP MBa |

| |

IP MB_P W R | IP MB_P WRG OOD | |

| ||

FPGA2 |

| |

IP MBb |

| |

| SLOT a | |

| or | |

CMM 2 | CDMa | |

IP MB_ P W RG OOD | ||

IP MB_P W R | ||

SLOT b | ||

| or | |

FPGA1 | CDMb | |

| ||

IP MBa |

| |

IP MB_P W R | IP MB_P W RGO OD | |

| ||

FPGA2 |

| |

IP MBb |

|

4.13.2Dual Bus IPMB Isolation Requirements

The isolation requirements for a dual bus IPMB are more stringent. In addition to the power failure isolation needed by radial IPMBs, dual bus IPMBs must be able to selectively enable and disable the isolation on each bus. Furthermore, each element on the bus must protect against errors that can cause the bus to hang. Finally, there are electrical drive and rise time requirements that are more difficult to meet on a shared bus.

An LTC4300 on each bus provides the necessary individually selectable isolation mechanisms in addition to rise time acceleration. A watchdog timer is also used to ensure the bus is isolated if the CPU locks up and resets so that glitches are not propagated to other controllers on the bus. See Figure 6.

Intel NetStructure® MPCMM0002 Chassis Management Module |

|

Hardware TPS | July 2007 |

22 | Order Number: |