BASIC

INTERVAL

TIMER

![]() INTBT

INTBT

TI0/P13 ![]()

![]() TIMER/EVENT

TIMER/EVENT

PTO0/P20 ![]() COUNTER #0

COUNTER #0

| INTT0 | |

BUZ/P23 | WATCH | |

TIMER | ||

|

|

| PORT0 |

PROGRAM | SP(8) | PORT1 |

COUNTER(13) |

| |

CY |

| |

|

| |

| ALU | PORT2 |

|

| |

| BANK | PORT3 |

|

| |

|

| PORT4 |

PROGRAM |

|

|

MEMORY | GENERAL REG. | PORT5 |

4

4

4

4

4

4

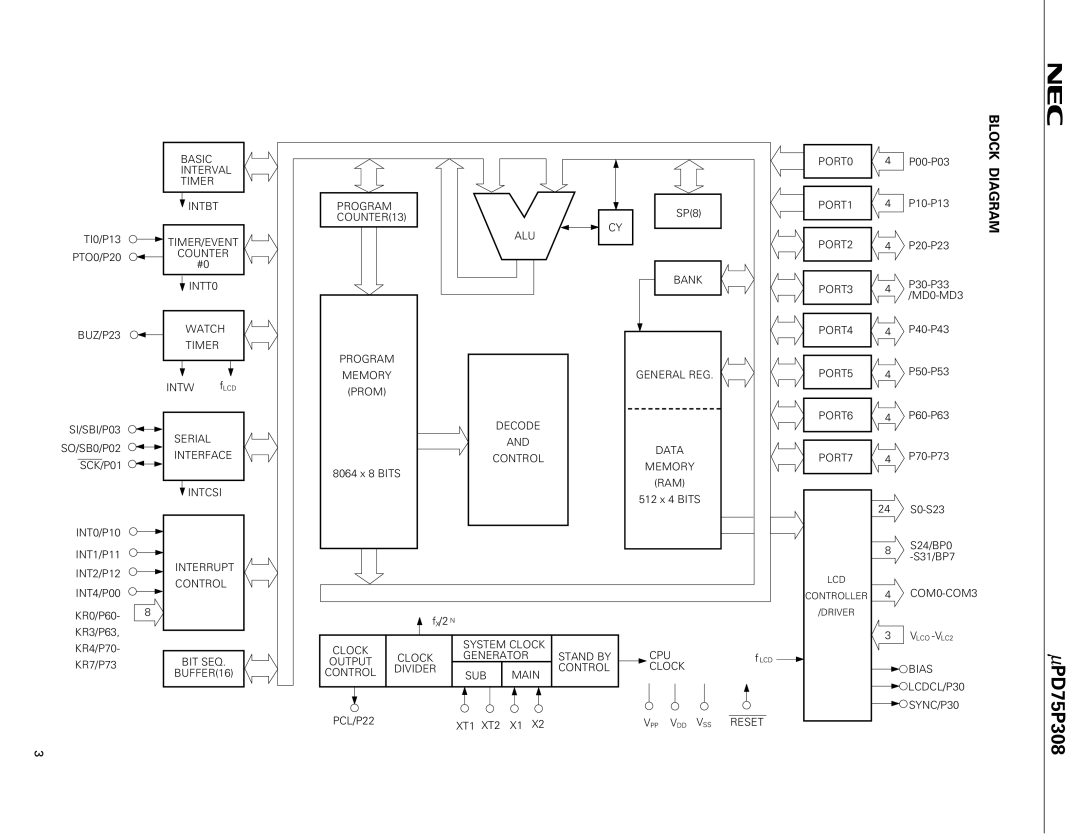

BLOCK DIAGRAM

SI/SBI/P03

SO/SB0/P02

SCK/P01

INTW fLCD

SERIAL

INTERFACE

![]() INTCSI

INTCSI

(PROM) |

|

| |

DECODE |

| PORT6 | |

|

| ||

AND | DATA |

| |

PORT7 | |||

CONTROL | |||

MEMORY | |||

8064 x 8 BITS |

| ||

(RAM) |

| ||

| |||

| 512 x 4 BITS | ||

4

4

24

INT0/P10

INT1/P11

INT2/P12

INT4/P00

KR0/P60- KR3/P63, KR4/P70- KR7/P73

8 ![]()

INTERRUPT

CONTROL

BIT SEQ.

BUFFER(16)

LCD |

CONTROLLER |

/DRIVER |

fX/2 N |

CLOCK |

| SYSTEM CLOCK |

|

| |||

CLOCK | GENERATOR | STAND BY | CPU | fLCD | |||

OUTPUT | |||||||

DIVIDER |

|

| CONTROL | CLOCK |

| ||

CONTROL | SUB |

|

| ||||

| MAIN |

|

| ||||

PCL/P22 |

| XT1 XT2 | X1 | X2 | VPP VDD VSS | RESET | |

8S24/BP0 ![]()

4

3VLCO

![]() BIAS

BIAS

![]() LCDCL/P30

LCDCL/P30

![]() SYNC/P30

SYNC/P30

μPD75P308

3