Peripheral Architecture | www.ti.com |

2.9Self-Refresh Mode

Setting the self refresh (SR) bit in the SDRAM refresh control register (SDRFC) to 1 forces the DDR2 memory controller to place the external DDR2 SDRAM in a

The DDR2 memory controller exits the

The DDR2 memory controller will not exit the

After exiting from the

2.10Reset Considerations

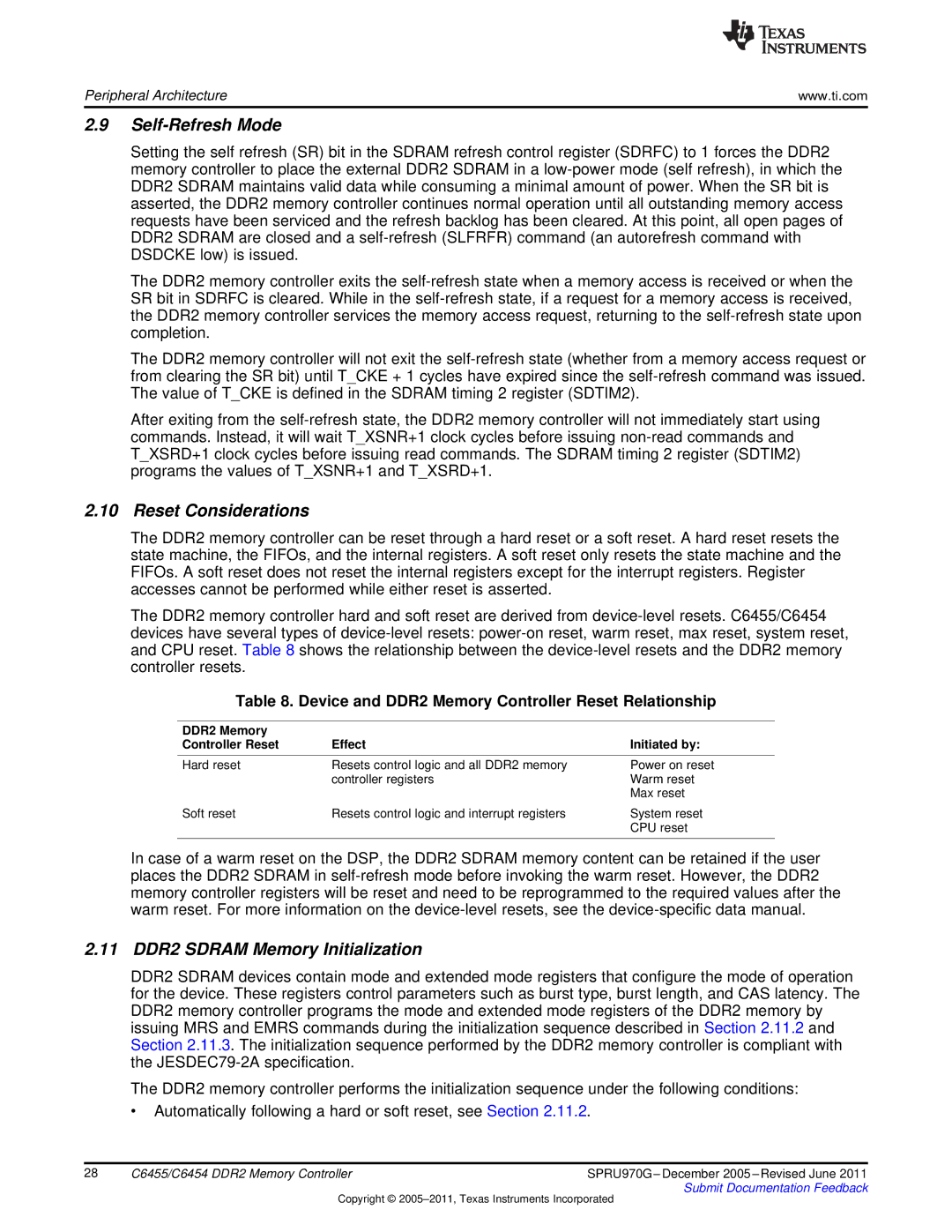

The DDR2 memory controller can be reset through a hard reset or a soft reset. A hard reset resets the state machine, the FIFOs, and the internal registers. A soft reset only resets the state machine and the FIFOs. A soft reset does not reset the internal registers except for the interrupt registers. Register accesses cannot be performed while either reset is asserted.

The DDR2 memory controller hard and soft reset are derived from

Table 8. Device and DDR2 Memory Controller Reset Relationship

DDR2 Memory |

|

|

Controller Reset | Effect | Initiated by: |

|

|

|

Hard reset | Resets control logic and all DDR2 memory | Power on reset |

| controller registers | Warm reset |

|

| Max reset |

Soft reset | Resets control logic and interrupt registers | System reset |

|

| CPU reset |

|

|

|

In case of a warm reset on the DSP, the DDR2 SDRAM memory content can be retained if the user places the DDR2 SDRAM in

2.11 DDR2 SDRAM Memory Initialization

DDR2 SDRAM devices contain mode and extended mode registers that configure the mode of operation for the device. These registers control parameters such as burst type, burst length, and CAS latency. The DDR2 memory controller programs the mode and extended mode registers of the DDR2 memory by issuing MRS and EMRS commands during the initialization sequence described in Section 2.11.2 and Section 2.11.3. The initialization sequence performed by the DDR2 memory controller is compliant with the

The DDR2 memory controller performs the initialization sequence under the following conditions:

•Automatically following a hard or soft reset, see Section 2.11.2.

28 | C6455/C6454 DDR2 Memory Controller | SPRU970G – December 2005 – Revised June 2011 |

|

| Submit Documentation Feedback |

Copyright ©