www.ti.com | DDR2 Memory Controller Registers |

4.1Module ID and Revision Register (MIDR)

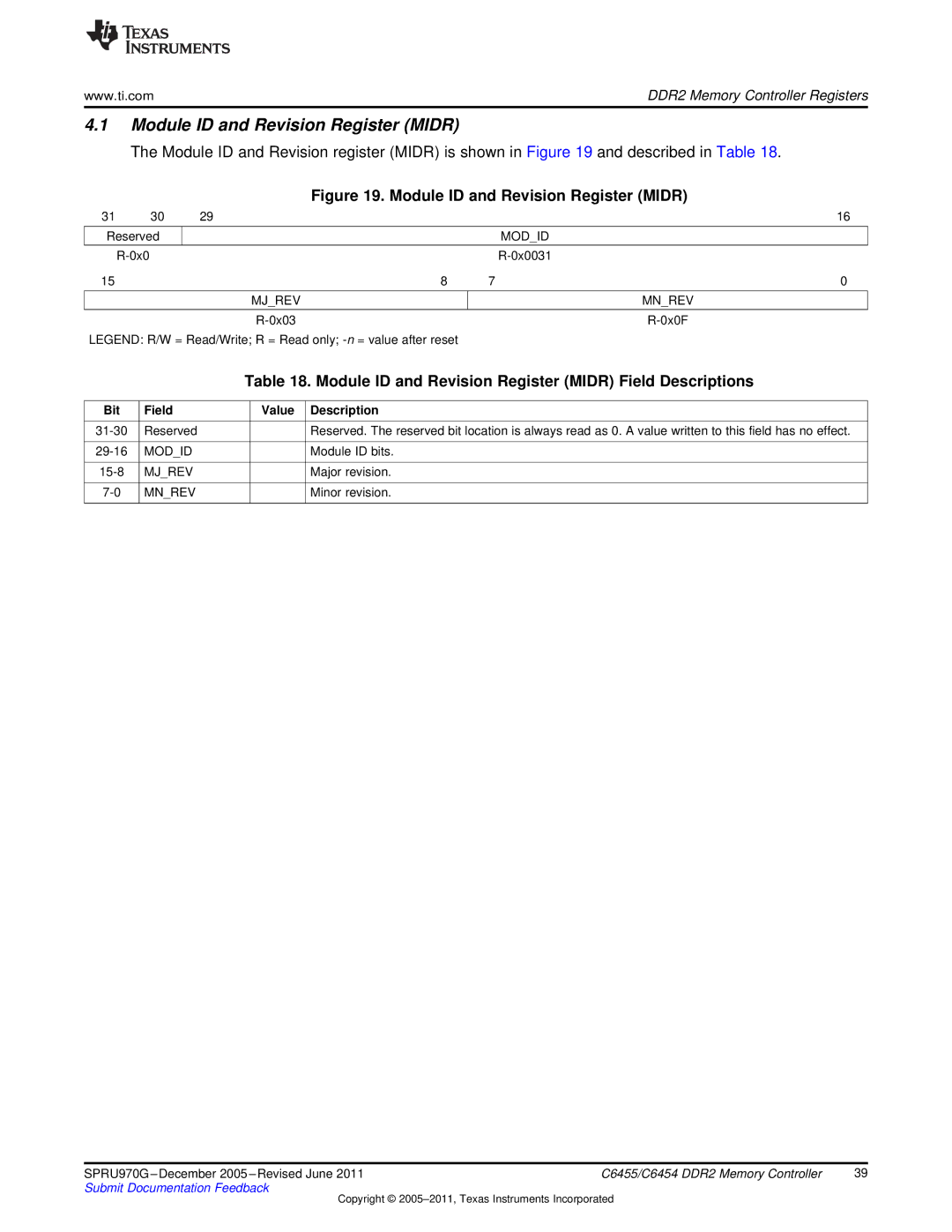

The Module ID and Revision register (MIDR) is shown in Figure 19 and described in Table 18.

Figure 19. Module ID and Revision Register (MIDR)

31 | 30 | 29 |

| 16 |

Reserved |

|

| MOD_ID | |

|

|

|

|

|

|

|

| ||

15 |

| 8 | 7 | 0 |

|

|

|

|

|

|

| MJ_REV |

| MN_REV |

|

|

|

|

|

|

|

| ||

LEGEND: R/W = Read/Write; R = Read only; |

|

| ||

|

| Table 18. Module ID and Revision Register (MIDR) Field Descriptions | ||

|

|

|

| |

Bit | Field |

| Value | Description |

|

|

|

|

|

Reserved |

|

| Reserved. The reserved bit location is always read as 0. A value written to this field has no effect. | |

|

|

|

|

|

MOD_ID |

|

| Module ID bits. | |

|

|

|

|

|

MJ_REV |

|

| Major revision. | |

|

|

|

|

|

MN_REV |

|

| Minor revision. | |

|

|

|

|

|

SPRU970G – December 2005 – Revised June 2011 | C6455/C6454 DDR2 Memory Controller | 39 |

Submit Documentation Feedback |

|

|

Copyright ©