DDR2 Memory Controller Registers | www.ti.com |

4.5SDRAM Timing 1 Register (SDTIM1)

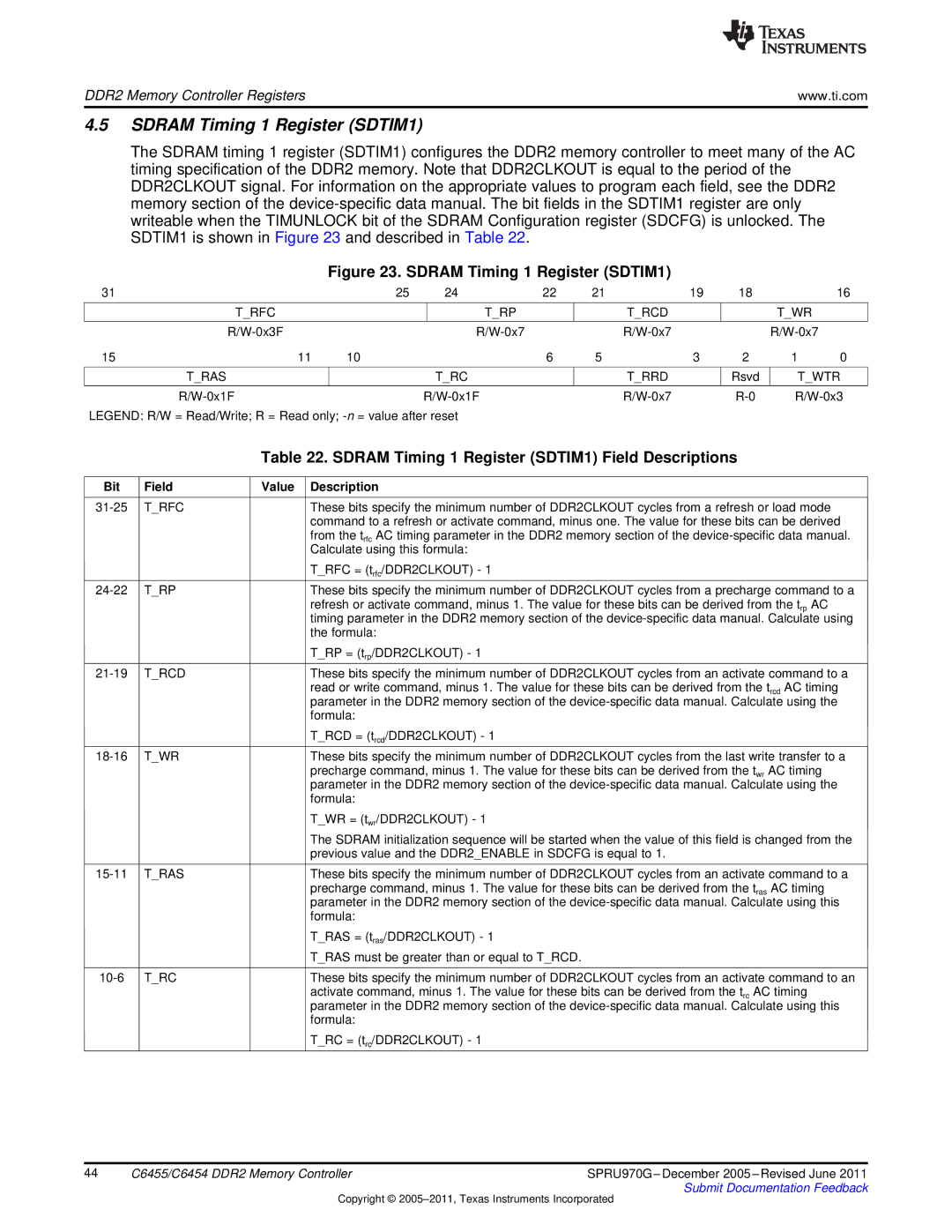

The SDRAM timing 1 register (SDTIM1) configures the DDR2 memory controller to meet many of the AC timing specification of the DDR2 memory. Note that DDR2CLKOUT is equal to the period of the DDR2CLKOUT signal. For information on the appropriate values to program each field, see the DDR2 memory section of the

Figure 23. SDRAM Timing 1 Register (SDTIM1)

31 |

| 25 | 24 | 22 | 21 | 19 | 18 |

| 16 | |

T_RFC |

|

|

| T_RP |

| T_RCD |

|

| T_WR |

|

|

|

|

|

|

|

| ||||

15 | 11 | 10 |

|

| 6 | 5 | 3 | 2 | 1 | 0 |

|

|

|

|

|

|

|

|

|

| |

T_RAS |

|

|

| T_RC |

| T_RRD |

| Rsvd | T_WTR | |

|

|

|

| |||||||

LEGEND: R/W = Read/Write; R = Read only; |

|

|

|

|

|

| ||||

|

| Table 22. SDRAM Timing 1 Register (SDTIM1) Field Descriptions | |

|

|

| |

Bit | Field | Value | Description |

|

|

|

|

T_RFC |

| These bits specify the minimum number of DDR2CLKOUT cycles from a refresh or load mode | |

|

|

| command to a refresh or activate command, minus one. The value for these bits can be derived |

|

|

| from the trfc AC timing parameter in the DDR2 memory section of the |

|

|

| Calculate using this formula: |

|

|

| T_RFC = (trfc/DDR2CLKOUT) - 1 |

|

|

|

|

T_RP |

| These bits specify the minimum number of DDR2CLKOUT cycles from a precharge command to a | |

|

|

| refresh or activate command, minus 1. The value for these bits can be derived from the trp AC |

|

|

| timing parameter in the DDR2 memory section of the |

|

|

| the formula: |

|

|

| T_RP = (trp/DDR2CLKOUT) - 1 |

|

|

|

|

T_RCD |

| These bits specify the minimum number of DDR2CLKOUT cycles from an activate command to a | |

|

|

| read or write command, minus 1. The value for these bits can be derived from the trcd AC timing |

|

|

| parameter in the DDR2 memory section of the |

|

|

| formula: |

|

|

| T_RCD = (trcd/DDR2CLKOUT) - 1 |

|

|

|

|

T_WR |

| These bits specify the minimum number of DDR2CLKOUT cycles from the last write transfer to a | |

|

|

| precharge command, minus 1. The value for these bits can be derived from the twr AC timing |

|

|

| parameter in the DDR2 memory section of the |

|

|

| formula: |

|

|

| T_WR = (twr/DDR2CLKOUT) - 1 |

|

|

| The SDRAM initialization sequence will be started when the value of this field is changed from the |

|

|

| previous value and the DDR2_ENABLE in SDCFG is equal to 1. |

|

|

|

|

T_RAS |

| These bits specify the minimum number of DDR2CLKOUT cycles from an activate command to a | |

|

|

| precharge command, minus 1. The value for these bits can be derived from the tras AC timing |

|

|

| parameter in the DDR2 memory section of the |

|

|

| formula: |

|

|

| T_RAS = (tras/DDR2CLKOUT) - 1 |

|

|

| T_RAS must be greater than or equal to T_RCD. |

|

|

|

|

T_RC |

| These bits specify the minimum number of DDR2CLKOUT cycles from an activate command to an | |

|

|

| activate command, minus 1. The value for these bits can be derived from the trc AC timing |

|

|

| parameter in the DDR2 memory section of the |

|

|

| formula: |

|

|

| T_RC = (trc/DDR2CLKOUT) - 1 |

|

|

|

|

44 | C6455/C6454 DDR2 Memory Controller | SPRU970G – December 2005 – Revised June 2011 |

|

| Submit Documentation Feedback |

Copyright ©