www.ti.com | DDR2 Memory Controller Registers |

4.7Burst Priority Register (BPRIO)

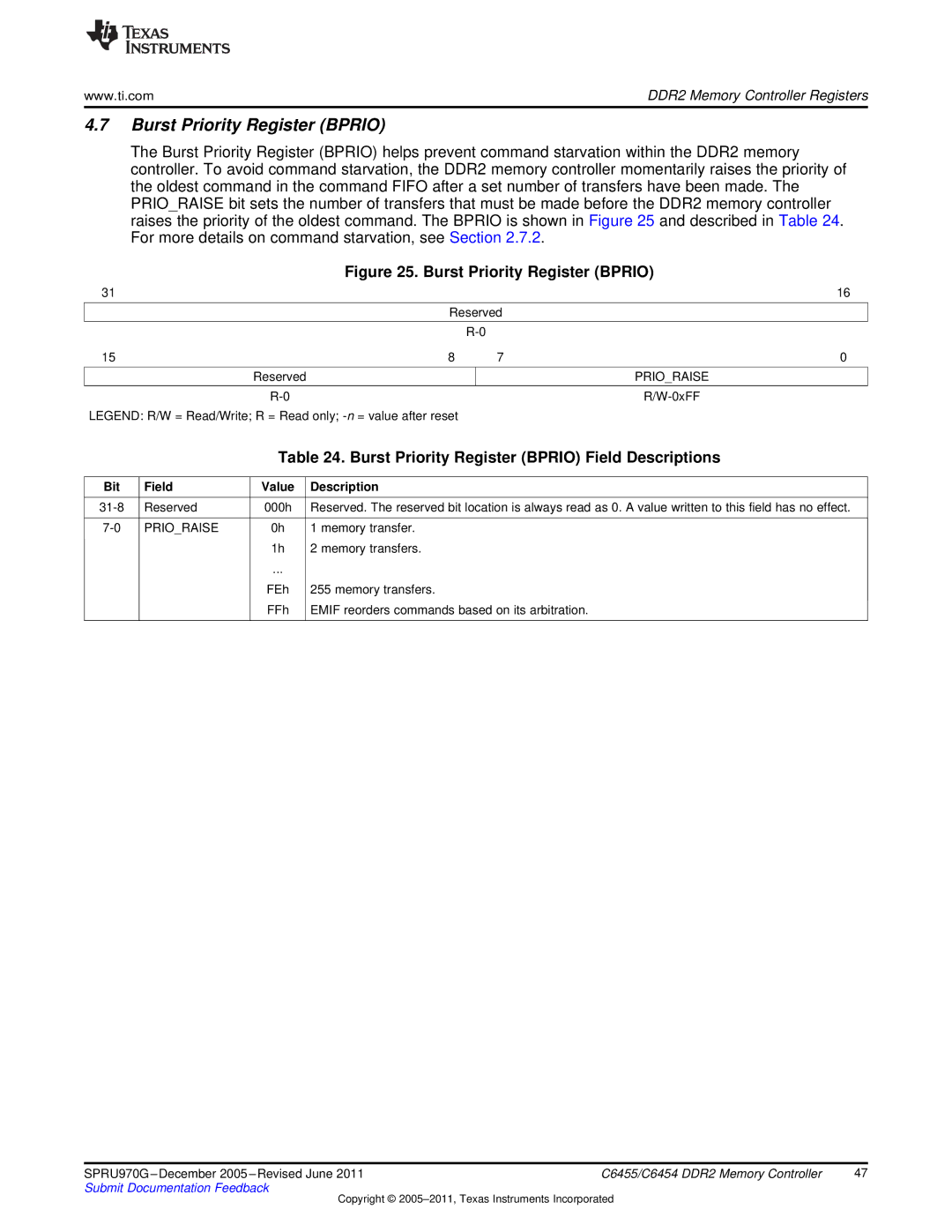

The Burst Priority Register (BPRIO) helps prevent command starvation within the DDR2 memory controller. To avoid command starvation, the DDR2 memory controller momentarily raises the priority of the oldest command in the command FIFO after a set number of transfers have been made. The PRIO_RAISE bit sets the number of transfers that must be made before the DDR2 memory controller raises the priority of the oldest command. The BPRIO is shown in Figure 25 and described in Table 24. For more details on command starvation, see Section 2.7.2.

Figure 25. Burst Priority Register (BPRIO)

31 |

|

|

| 16 |

| Reserved |

| ||

|

|

| ||

15 | 8 | 7 | 0 | |

|

|

|

|

|

Reserved |

|

|

| PRIO_RAISE |

|

|

| ||

LEGEND: R/W = Read/Write; R = Read only;

Table 24. Burst Priority Register (BPRIO) Field Descriptions

Bit | Field | Value | Description |

|

|

|

|

Reserved | 000h | Reserved. The reserved bit location is always read as 0. A value written to this field has no effect. | |

|

|

|

|

PRIO_RAISE | 0h | 1 memory transfer. | |

|

| 1h | 2 memory transfers. |

|

| ... |

|

|

| FEh | 255 memory transfers. |

|

| FFh | EMIF reorders commands based on its arbitration. |

|

|

|

|

SPRU970G – December 2005 – Revised June 2011 | C6455/C6454 DDR2 Memory Controller | 47 |

Submit Documentation Feedback |

|

|

Copyright ©