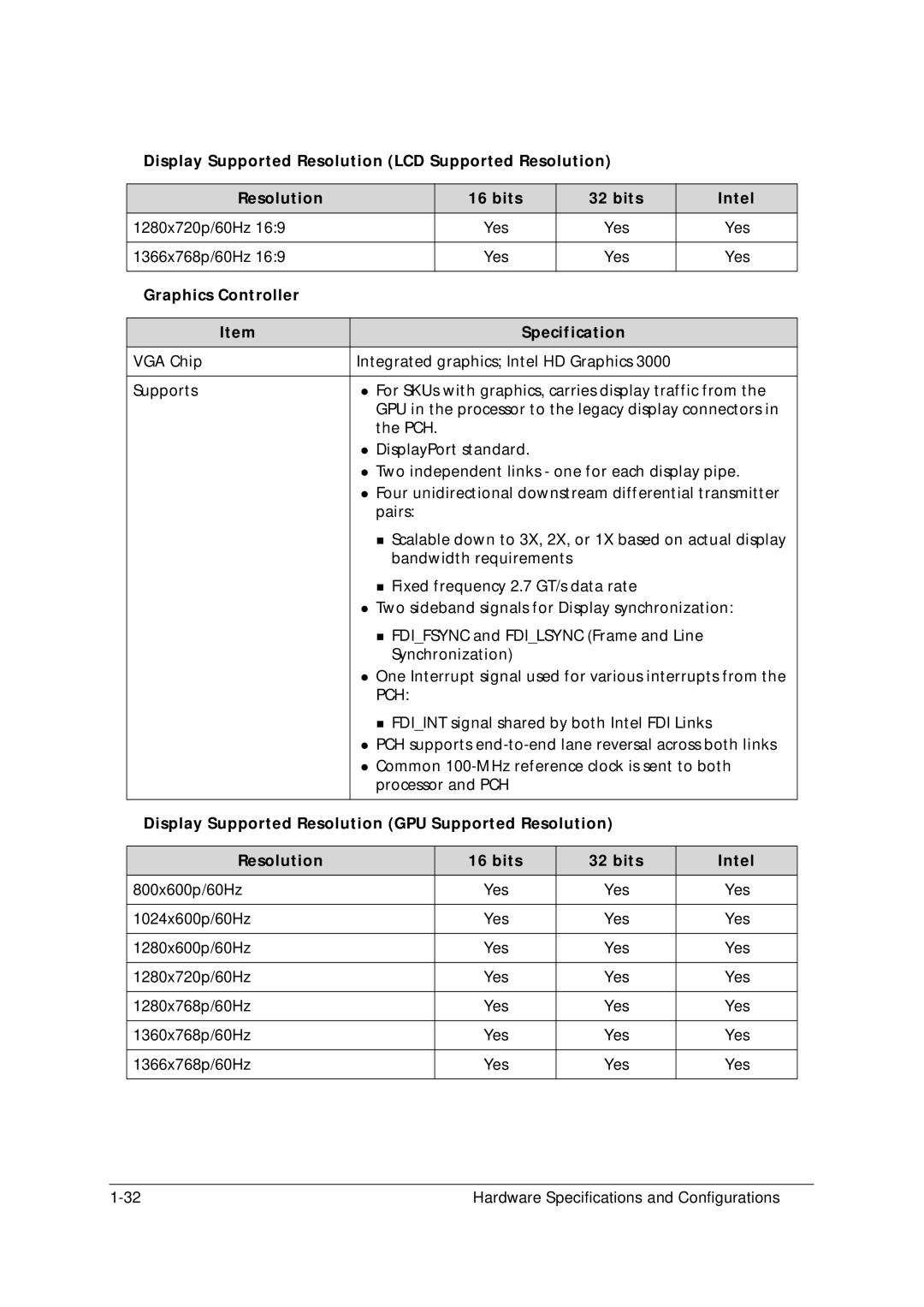

Display Supported Resolution (LCD Supported Resolution)

Resolution |

| 16 bits |

| 32 bits |

| Intel |

|

|

|

|

|

|

|

1280x720p/60Hz 16:9 |

| Yes |

| Yes |

| Yes |

|

|

|

|

|

|

|

1366x768p/60Hz 16:9 |

| Yes |

| Yes |

| Yes |

|

|

|

|

|

|

|

Graphics Controller |

|

|

|

|

|

|

|

|

|

|

|

| |

Item |

| Specification |

| |||

|

|

|

|

|

| |

VGA Chip | Integrated graphics; Intel HD Graphics 3000 |

| ||||

|

| |||||

Supports | For SKUs with graphics, carries display traffic from the | |||||

| GPU in the processor to the legacy display connectors in | |||||

| the PCH. |

|

|

| ||

| DisplayPort standard. |

|

|

| ||

| Two independent links - one for each display pipe. | |||||

| Four unidirectional downstream differential transmitter | |||||

| pairs: |

|

|

| ||

| Scalable down to 3X, 2X, or 1X based on actual display | |||||

| bandwidth requirements |

|

|

| ||

| Fixed frequency 2.7 GT/s data rate |

| ||||

| Two sideband signals for Display synchronization: | |||||

| FDI_FSYNC and FDI_LSYNC (Frame and Line |

| ||||

| Synchronization) |

|

|

| ||

| One Interrupt signal used for various interrupts from the | |||||

| PCH: |

|

|

| ||

| FDI_INT signal shared by both Intel FDI Links |

| ||||

| PCH supports | |||||

| Common | |||||

| processor and PCH |

|

|

| ||

|

|

| ||||

Display Supported Resolution (GPU Supported Resolution) |

| |||||

|

|

|

|

|

|

|

Resolution |

| 16 bits |

| 32 bits |

| Intel |

|

|

|

|

|

|

|

800x600p/60Hz |

| Yes |

| Yes |

| Yes |

|

|

|

|

|

|

|

1024x600p/60Hz |

| Yes |

| Yes |

| Yes |

|

|

|

|

|

|

|

1280x600p/60Hz |

| Yes |

| Yes |

| Yes |

|

|

|

|

|

|

|

1280x720p/60Hz |

| Yes |

| Yes |

| Yes |

|

|

|

|

|

|

|

1280x768p/60Hz |

| Yes |

| Yes |

| Yes |

|

|

|

|

|

|

|

1360x768p/60Hz |

| Yes |

| Yes |

| Yes |

|

|

|

|

|

|

|

1366x768p/60Hz |

| Yes |

| Yes |

| Yes |

|

|

|

|

|

|

|

Hardware Specifications and Configurations |