Programming Guide

Printing History

Safety Guidelines

Table of Contents

Internally Triggered Measurements

Language Dictionary

Output Commands

Scpi Conformance Information

Error Messages

Compatibility Language

Example Programs

Documentation Summary

About this Guide

External References

Gpib References

Scpi References

Downloading and Installing the Driver

VXIplug&play Power Products Instrument Drivers

Supported Applications

System Requirements

Gpib Capabilities of the DC Source

Accessing Online Help

RS-232 Capabilities of the DC Source

Gpib Address

RS-232 Flow Control

RS-232 Programming Example

Baud Rate

Introduction to Scpi

RS-232 Troubleshooting

Conventions Used in This Guide

Boldface font

Multiple Commands in a Message

Types of Scpi Commands

Using Queries

Including Common Commands

Types of Scpi Messages

Moving Among Subsystems

Message Unit

Query Indicator

Headers

Message Unit Separator

Numerical Data Formats

Scpi Data Formats

Suffixes and Multipliers

Response Data Types

Using Device Clear

Scpi Command Completion

Page

Introduction

Power-on Initialization

Programming the Output

Enabling the Output

Output Current

Output Voltage

Maximum Voltage

Maximum Current

Triggering Output Changes

Setting the Voltage or Current Trigger Levels

Scpi Triggering Nomenclature

Output Trigger System Model

Generating Triggers

Initiating the Output Trigger System

Making Measurements

Voltage and Current Measurements

DC Measurements

Current Ranges

RMS Measurements Agilent 66312A, 66332A Only

Internally Triggered Measurements

Measurement Trigger System Model

Sequence Form Alias SEQuence2 ACQuire

BUS

Generating Measurement Triggers Agilent 66312A, 66332A Only

Trigger Commands Used to Measure Output Pulses

Measuring Output Pulses Agilent 66312A, 66332A Only

Current Detector

Pulse Measurement Queries

Controlling Measurement Samples

Varying the Voltage or Current Sampling Rate

Multiple Measurements Agilent 66312A, 66332A Only

Pre-event and Post-event Triggering

Pulse Measurement Example Agilent 66312A, 66332A only

Option Base

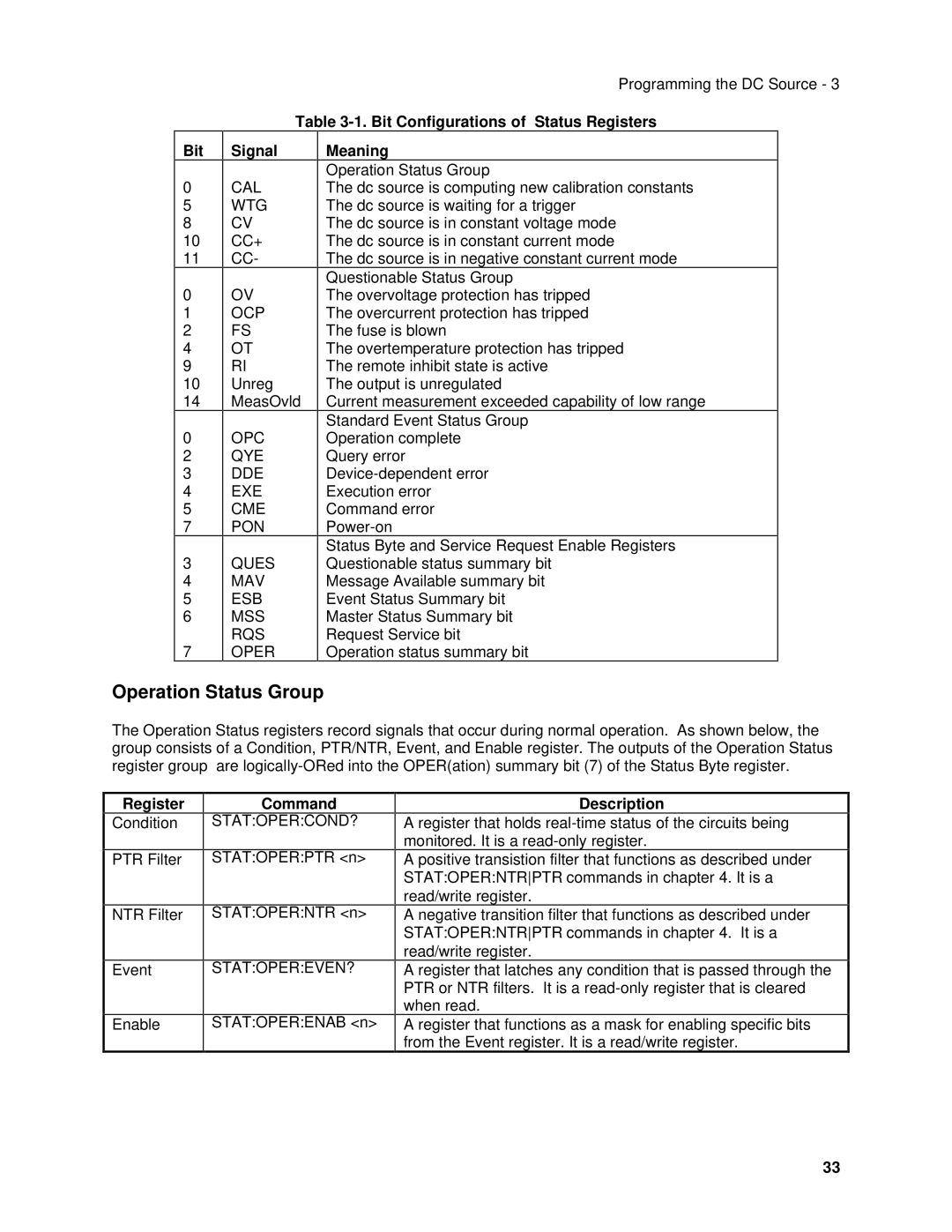

Programming the Status Registers

Power-On Conditions

Operation Status Group

Questionable Status Group

Standard Event Status Group

Status Byte Register

Servicing Operation Status and Questionable Status Events

Determining the Cause of a Service Interrupt

MSS Bit

RQS Bit

Monitoring Both Phases of a Status Transition

Inhibit/Fault Indicator

Discrete Fault Indicator DFI

Remote Inhibit RI

Bit Weight

Using the Inhibit/Fault Port as a Digital I/O

DFI Programming Example

Pin

Page

Language Dictionary

Subsystem Commands

Subsystem Commands Syntax

ALC

DFI

Subsystem Commands Syntax

Common Commands Syntax

Common Commands

Programming Parameters

Output Programming Parameters

CALibrateCURRent

Calibration Commands

CALibrateCURRentNEGative

CALibrateCURRentMEASureLOWRange

Command Syntax CALibrateSAVE Parameters None Examples

CALibratePASSword

CALibrateDATA

CALibrateLEVel

CALibrateVOLTage

CALibrateSTATe

CALibrateVOLTagePROTection

Query Syntax CALibrateSTATe?

MEASureARRayCURRent? FETChARRayCURRent?

Measurement Commands

MEASureARRayVOLTage? FETChARRayVOLTage?

Query Syntax

MEASureCURRentACDC? FETChCURRentACDC?

MEASureCURRent? FETChCURRent?

MEASureCURRentHIGH? FETChCURRentHIGH?

FETChCURRent? applies to Agilent 66312A, 66332A Only

MEASureCURRentLOW? FETChCURRentLOW?

MEASureCURRentMAXimum? FETChCURRent MAXimum?

MEASureCURRentMINimum? FETChCURRentMINimum?

MEASureVOLTageACDC? FETChVOLTageACDC?

MEASureVOLTage? FETChVOLTage?

MEASureVOLTageHIGH? FETChVOLTageHIGH?

FETChVOLTage? applies to Agilent 66312A, 66332A Only

MEASureVOLTageLOW? FETChVOLTageLOW?

MEASureVOLTageMAXimum? FETChVOLTageMAXimum?

MEASureVOLTageMINimum? FETChVOLTageMINimum?

SENSeCURRentDETector

SENSeCURRentRANGe

Unit a amperes *RST Value MAX high range

Returned Parameters NR3

SENSeSWEepOFFSetPOINts

SENSeFUNCtion

SENSeSWEepPOINts

SENSeSWEepTINTerval

HANNing

SENSeWINDow

RECTangular

Returned Parameters CRD

OUTPut

Output Commands

OUTPutDFI

OUTPutDFISOURce

OUTPutPROTectionDELay

OUTPutPONSTATe

OUTPutPROTectionCLEar

OUTPutRELayPOLarity

OUTPutRELay

OUTPutRIMODE

Query Syntax OUTPputRELayPOLarity?

SOURceCURRent

Default Suffix

SOURceCURRentTRIGger

SOURceCURRentPROTectionSTATe

SOURceDIGitalFUNCtion

SOURceDIGitalDATA

SOURceVOLTage

Query Syntax SOURceDIGitalDATA?

SOURceVOLTageTRIGger

SOURceVOLTageALCBANDwidth? SOURceVOLTageALCBWIDth?

SOURceVOLTagePROTection

Agilent 66332A, 6631B, 6632B, 6633B and 6634B Only

STATusPRESet

Status Commands

STATusOPERation?

STATusOPERationCONDition?

Query Syntax STATusOPERationENABle?

STATusOPERationENABle

Parameters Preset Value

STATusOPERationNTR STATusOPERationPTR

STATusQUEStionableENABle

STATusQUEStionable?

STATusQUEStionableCONDition?

STATusQUEStionableNTR STATusQUEStionablePTR

Command Syntax *CLS Parameters None

CLS

STATQUESNTR?STATQUESPTR?

ESE

Bit Configuration of Standard Event Status Enable Register

ESR?

OPC

SRE

PSC

PSC on

Example

STB?

Bit Configuration of Status Byte Register

WAI

NR1 register binary value

DISPlay

System Commands

DISPlayMODE

DISPlayTEXT

SYSTemLANGuage

SYSTemERRor?

SYSTemVERSion?

Parameters none Returned Parameters NR2

SYSTemREMote

SYSTemLOCal

SYSTemRWLock

IDN?

OPT?

Command Syntax RCL NRf Parameters Example

RCL

RST

Command Syntax SAV NRf Parameters Example

RST Settings

SAV

TST?

ABORt

Trigger Commands

INITiateSEQuence INITiateNAME

INITiateCONTinuousSEQuence1 INITiateCONTinuousNAME

TRIGgerSOURce

TRIGger

TRIGgerSEQuence2 TRIGgerACQuire

Abor Currtrig Init *TRG Volttrig

TRIGgerSEQuence2COUNtVOLTage TRIGgerACQuireCOUNtVOLTage

TRIGgerSEQuence2COUNtCURRent TRIGgerACQuireCOUNtCURRent

Parameters RST Value Examples

TRIGSEQ2COUNCURR 5 Trigacqcouncurr

TRIGSEQ2HYSTCURR TRIGSEQ2LEVVOLT

TRIGSEQ2HYSTVOLT TRIGSEQ2LEVCURR

TRIGgerSEQuence2LEVelVOLTage TRIGgerACQuireLEVelVOLTage

TRIGgerSEQuence2LEVelCURRent TRIGgerACQuireLEVelCURRent

TRIGSEQ2LEVVOLT TRIGSEQ2HYSTCURR

TRIGSEQ2LEVCURR TRIGSEQ2HYSTVOLT

TRIGgerSEQuence2SLOPeCURRent TRIGgerACQuireSLOPeCURRent

TRIGgerSEQuence2SLOPeVOLTage TRIGgerACQuireSLOPeVOLTage

TRIGSEQ2SLOPVOLT

TRIGgerSEQuence2SOURce TRIGgerACQuireSOURce

Parameters None Related Commands

TRIGgerSEQuence1DEFine TRIGgerSEQuence2DEFine

TRG

Page

Scpi Confirmed Commands

Non-SCPI Commands

Scpi Version

Page

Command Setting

Table B-1. COMPatibility Power-on Settings Command

ERR? FAULT? ID? IOUT?

Table B-2. COMPatibility Commands Compatibility

Similar Scpi Command

ASTS? CLR

Table B-2. COMPatibility Commands Description Similar Scpi

Compatibility Command

Compatibility Description Command

Table B-2. COMPatibility Commands

These commands determine the conditions that will set bits

Error

Norm Fast INH ERR UNR +CC

RQS ERR RDY

FAU

Page

Bit Set Error Number Error Code Error Type

Error Number List

Table C-1. Error Numbers

Error Number

Page

Types of DOS Drivers

Assigning the Gpib Address in Programs

Agilent 82335A Driver

National Instruments Gpib Driver

Basic Controllers

Error Handling

Example Programs D

Call IBCLRPS%

Example 2. IBM Controller Using National Interface

CODES$=*CLS

Option Base

Example 3. Controller Using Basic

Index

100

Index

Scpi

101

102

Manual Updates