CY7C68033/CY7C68034

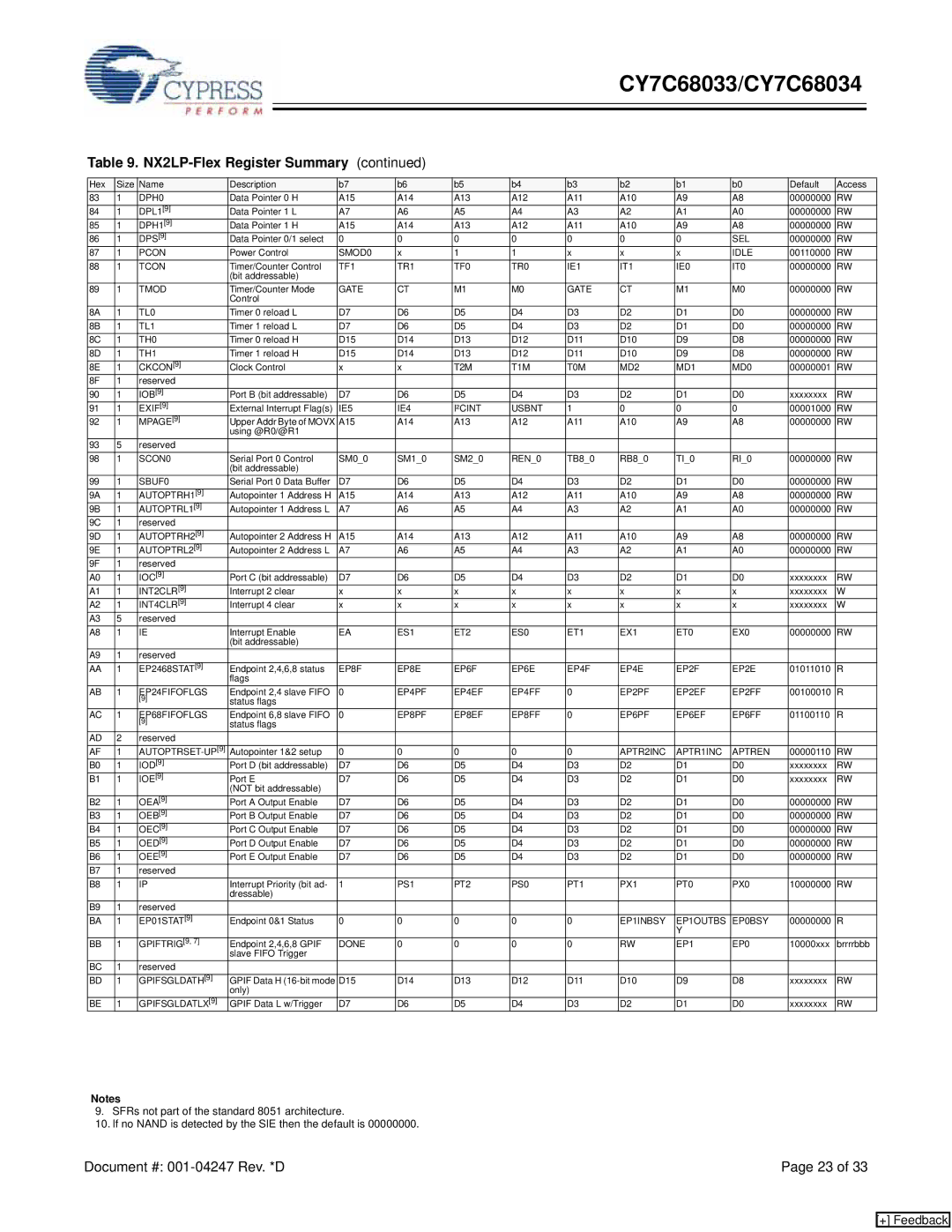

Table 9. NX2LP-Flex Register Summary (continued)

Hex | Size | Name | Description | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 | Default | Access |

83 | 1 | DPH0 | Data Pointer 0 H | A15 | A14 | A13 | A12 | A11 | A10 | A9 | A8 | 00000000 | RW |

84 | 1 | DPL1[9] | Data Pointer 1 L | A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 | 00000000 | RW |

85 | 1 | DPH1[9] | Data Pointer 1 H | A15 | A14 | A13 | A12 | A11 | A10 | A9 | A8 | 00000000 | RW |

86 | 1 | DPS[9] | Data Pointer 0/1 select | 0 | 0 | 0 | 0 | 0 | 0 | 0 | SEL | 00000000 | RW |

87 | 1 | PCON | Power Control | SMOD0 | x | 1 | 1 | x | x | x | IDLE | 00110000 | RW |

88 | 1 | TCON | Timer/Counter Control | TF1 | TR1 | TF0 | TR0 | IE1 | IT1 | IE0 | IT0 | 00000000 | RW |

|

|

| (bit addressable) |

|

|

|

|

|

|

|

|

|

|

89 | 1 | TMOD | Timer/Counter Mode | GATE | CT | M1 | M0 | GATE | CT | M1 | M0 | 00000000 | RW |

|

|

| Control |

|

|

|

|

|

|

|

|

|

|

8A | 1 | TL0 | Timer 0 reload L | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | 00000000 | RW |

8B | 1 | TL1 | Timer 1 reload L | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | 00000000 | RW |

8C | 1 | TH0 | Timer 0 reload H | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | 00000000 | RW |

8D | 1 | TH1 | Timer 1 reload H | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | 00000000 | RW |

8E | 1 | CKCON[9] | Clock Control | x | x | T2M | T1M | T0M | MD2 | MD1 | MD0 | 00000001 | RW |

8F | 1 | reserved |

|

|

|

|

|

|

|

|

|

|

|

90 | 1 | IOB[9] | Port B (bit addressable) | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | xxxxxxxx | RW |

91 | 1 | EXIF[9] | External Interrupt Flag(s) | IE5 | IE4 | I²CINT | USBNT | 1 | 0 | 0 | 0 | 00001000 | RW |

92 | 1 | MPAGE[9] | Upper Addr Byte of MOVX | A15 | A14 | A13 | A12 | A11 | A10 | A9 | A8 | 00000000 | RW |

|

|

| using @R0/@R1 |

|

|

|

|

|

|

|

|

|

|

93 | 5 | reserved |

|

|

|

|

|

|

|

|

|

|

|

98 | 1 | SCON0 | Serial Port 0 Control | SM0_0 | SM1_0 | SM2_0 | REN_0 | TB8_0 | RB8_0 | TI_0 | RI_0 | 00000000 | RW |

|

|

| (bit addressable) |

|

|

|

|

|

|

|

|

|

|

99 | 1 | SBUF0 | Serial Port 0 Data Buffer | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | 00000000 | RW |

9A | 1 | AUTOPTRH1[9] | Autopointer 1 Address H | A15 | A14 | A13 | A12 | A11 | A10 | A9 | A8 | 00000000 | RW |

9B | 1 | AUTOPTRL1[9] | Autopointer 1 Address L | A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 | 00000000 | RW |

9C | 1 | reserved |

|

|

|

|

|

|

|

|

|

|

|

9D | 1 | AUTOPTRH2[9] | Autopointer 2 Address H | A15 | A14 | A13 | A12 | A11 | A10 | A9 | A8 | 00000000 | RW |

9E | 1 | AUTOPTRL2[9] | Autopointer 2 Address L | A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 | 00000000 | RW |

9F | 1 | reserved |

|

|

|

|

|

|

|

|

|

|

|

A0 | 1 | IOC[9] | Port C (bit addressable) | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | xxxxxxxx | RW |

A1 | 1 | INT2CLR[9] | Interrupt 2 clear | x | x | x | x | x | x | x | x | xxxxxxxx | W |

A2 | 1 | INT4CLR[9] | Interrupt 4 clear | x | x | x | x | x | x | x | x | xxxxxxxx | W |

A3 | 5 | reserved |

|

|

|

|

|

|

|

|

|

|

|

A8 | 1 | IE | Interrupt Enable | EA | ES1 | ET2 | ES0 | ET1 | EX1 | ET0 | EX0 | 00000000 | RW |

|

|

| (bit addressable) |

|

|

|

|

|

|

|

|

|

|

A9 | 1 | reserved |

|

|

|

|

|

|

|

|

|

|

|

AA | 1 | EP2468STAT[9] | Endpoint 2,4,6,8 status | EP8F | EP8E | EP6F | EP6E | EP4F | EP4E | EP2F | EP2E | 01011010 | R |

|

|

| flags |

|

|

|

|

|

|

|

|

|

|

AB | 1 | EP24FIFOFLGS | Endpoint 2,4 slave FIFO | 0 | EP4PF | EP4EF | EP4FF | 0 | EP2PF | EP2EF | EP2FF | 00100010 | R |

|

| [9] | status flags |

|

|

|

|

|

|

|

|

|

|

AC | 1 | EP68FIFOFLGS | Endpoint 6,8 slave FIFO | 0 | EP8PF | EP8EF | EP8FF | 0 | EP6PF | EP6EF | EP6FF | 01100110 | R |

|

| [9] | status flags |

|

|

|

|

|

|

|

|

|

|

AD | 2 | reserved |

|

|

|

|

|

|

|

|

|

|

|

AF | 1 | Autopointer 1&2 setup | 0 | 0 | 0 | 0 | 0 | APTR2INC | APTR1INC | APTREN | 00000110 | RW | |

B0 | 1 | IOD[9] | Port D (bit addressable) | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | xxxxxxxx | RW |

B1 | 1 | IOE[9] | Port E | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | xxxxxxxx | RW |

|

|

| (NOT bit addressable) |

|

|

|

|

|

|

|

|

|

|

B2 | 1 | OEA[9] | Port A Output Enable | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | 00000000 | RW |

B3 | 1 | OEB[9] | Port B Output Enable | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | 00000000 | RW |

B4 | 1 | OEC[9] | Port C Output Enable | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | 00000000 | RW |

B5 | 1 | OED[9] | Port D Output Enable | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | 00000000 | RW |

B6 | 1 | OEE[9] | Port E Output Enable | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | 00000000 | RW |

B7 | 1 | reserved |

|

|

|

|

|

|

|

|

|

|

|

B8 | 1 | IP | Interrupt Priority (bit ad- | 1 | PS1 | PT2 | PS0 | PT1 | PX1 | PT0 | PX0 | 10000000 | RW |

|

|

| dressable) |

|

|

|

|

|

|

|

|

|

|

B9 | 1 | reserved |

|

|

|

|

|

|

|

|

|

|

|

BA | 1 | EP01STAT[9] | Endpoint 0&1 Status | 0 | 0 | 0 | 0 | 0 | EP1INBSY | EP1OUTBS | EP0BSY | 00000000 | R |

|

|

|

|

|

|

|

|

|

| Y |

|

|

|

BB | 1 | GPIFTRIG[9, 7] | Endpoint 2,4,6,8 GPIF | DONE | 0 | 0 | 0 | 0 | RW | EP1 | EP0 | 10000xxx | brrrrbbb |

|

|

| slave FIFO Trigger |

|

|

|

|

|

|

|

|

|

|

BC | 1 | reserved |

|

|

|

|

|

|

|

|

|

|

|

BD | 1 | GPIFSGLDATH[9] | GPIF Data H | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | xxxxxxxx | RW |

|

|

| only) |

|

|

|

|

|

|

|

|

|

|

BE | 1 | GPIFSGLDATLX[9] | GPIF Data L w/Trigger | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | xxxxxxxx | RW |

Notes

9.SFRs not part of the standard 8051 architecture.

10.If no NAND is detected by the SIE then the default is 00000000.

Document #: | Page 23 of 33 |

[+] Feedback