CY7C68033/CY7C68034

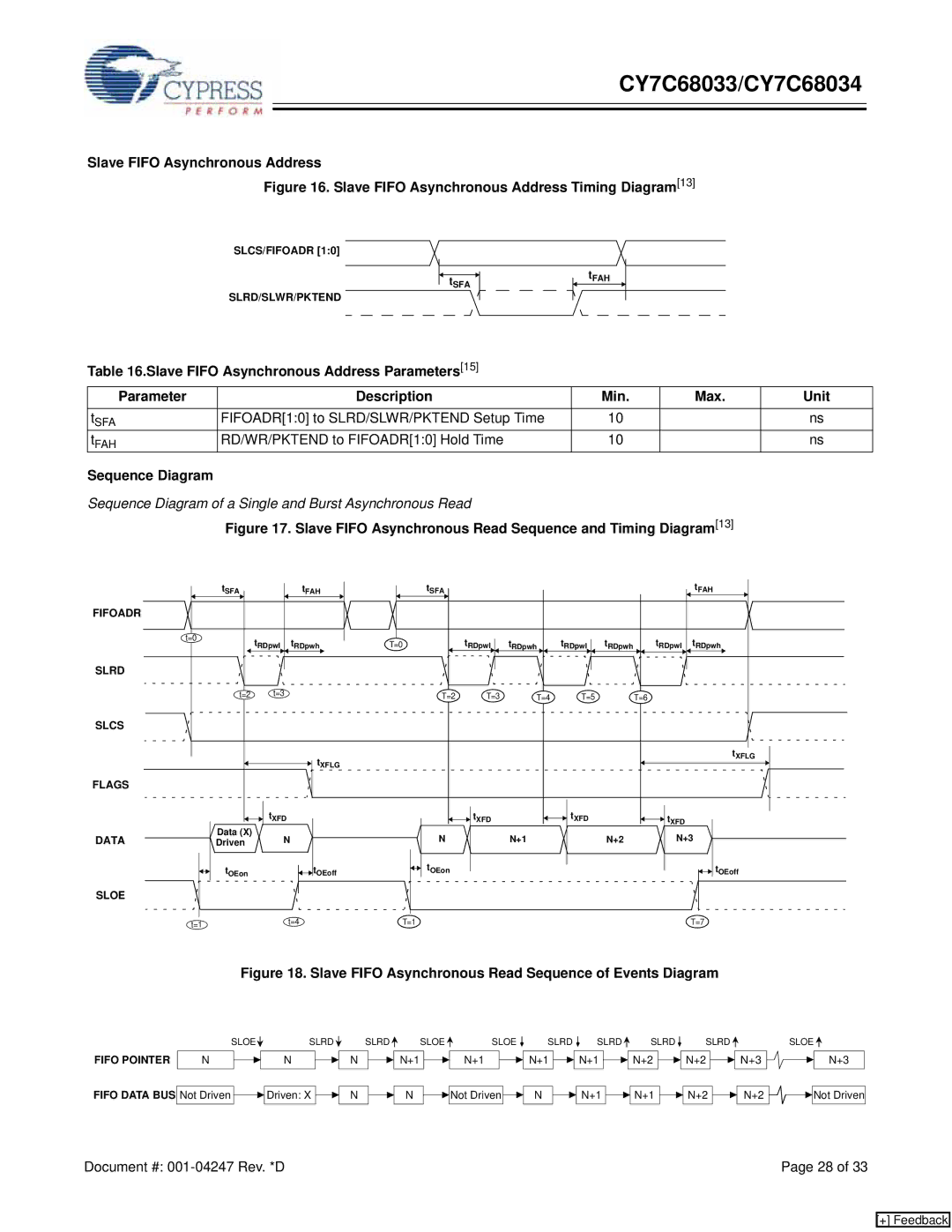

Slave FIFO Asynchronous Address

Figure 16. Slave FIFO Asynchronous Address Timing Diagram[13]

SLCS/FIFOADR [1:0]

tSFA

SLRD/SLWR/PKTEND

tFAH

Table 16.Slave FIFO Asynchronous Address Parameters[15]

Parameter | Description | Min. | Max. | Unit |

tSFA | FIFOADR[1:0] to SLRD/SLWR/PKTEND Setup Time | 10 |

| ns |

tFAH | RD/WR/PKTEND to FIFOADR[1:0] Hold Time | 10 |

| ns |

Sequence Diagram

Sequence Diagram of a Single and Burst Asynchronous Read

Figure 17. Slave FIFO Asynchronous Read Sequence and Timing Diagram[13]

|

|

|

|

|

| t |

| t |

|

|

|

| t | SFA |

|

|

|

|

|

|

|

|

| tFAH |

| |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||

|

|

|

|

|

| SFA |

| FAH |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

FIFOADR |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

| t=0 |

|

| tRDpwl |

| tRDpwh |

|

|

|

|

|

|

|

| tRDpwl |

| tRDpwh |

| tRDpwl |

| tRDpwh |

| tRDpwl tRDpwh |

| |||||||

|

|

|

|

|

|

|

|

|

| T=0 |

|

|

|

|

| |||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SLRD

t=2 | t=3 | T=2 | T=3 | T=4 | T=5 | T=6 |

SLCS

|

|

|

|

|

|

|

|

|

|

|

| tXFLG |

|

|

|

|

|

|

|

|

|

|

|

|

|

| tXFLG |

|

|

|

|

FLAGS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

| tXFD |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| tXFD |

| tXFD |

|

|

| t |

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| XFD |

|

|

|

|

|

| |

DATA |

|

|

| Data (X) |

| N |

|

|

| N |

|

|

| N+1 |

| N+2 |

|

| N+3 |

|

|

|

|

| |||||||

|

|

| Driven |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

| t |

|

|

|

| t | OEoff |

| tOEon |

|

|

|

|

|

|

|

|

|

|

|

| tOEoff |

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

|

|

| OEon |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

SLOE

t=1 | t=4 | T=1 | T=7 |

Figure 18. Slave FIFO Asynchronous Read Sequence of Events Diagram

FIFO POINTER

SLOE | SLRD |

| SLRD |

|

| SLOE |

| SLOE | SLRD |

| SLRD | SLRD | SLRD |

|

|

| SLOE |

|

| ||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

N |

|

| N |

|

| N |

|

|

|

| N+1 |

|

|

| N+1 |

|

|

| N+1 |

|

|

| N+1 |

|

| N+2 |

|

| N+2 |

|

| N+3 |

|

|

|

|

|

| N+3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||

FIFO DATA BUS

Not Driven |

|

| Driven: X |

|

| N |

|

|

|

|

|

|

N ![]()

![]()

![]() Not Driven

Not Driven ![]()

![]()

![]() N

N ![]()

![]()

![]() N+1

N+1 ![]()

![]()

![]() N+1

N+1 ![]()

![]()

![]() N+2

N+2 ![]()

![]()

![]() N+2

N+2 ![]()

![]()

![]()

![]()

![]() Not Driven

Not Driven

Document #: | Page 28 of 33 |

[+] Feedback