CY7C68033/CY7C68034

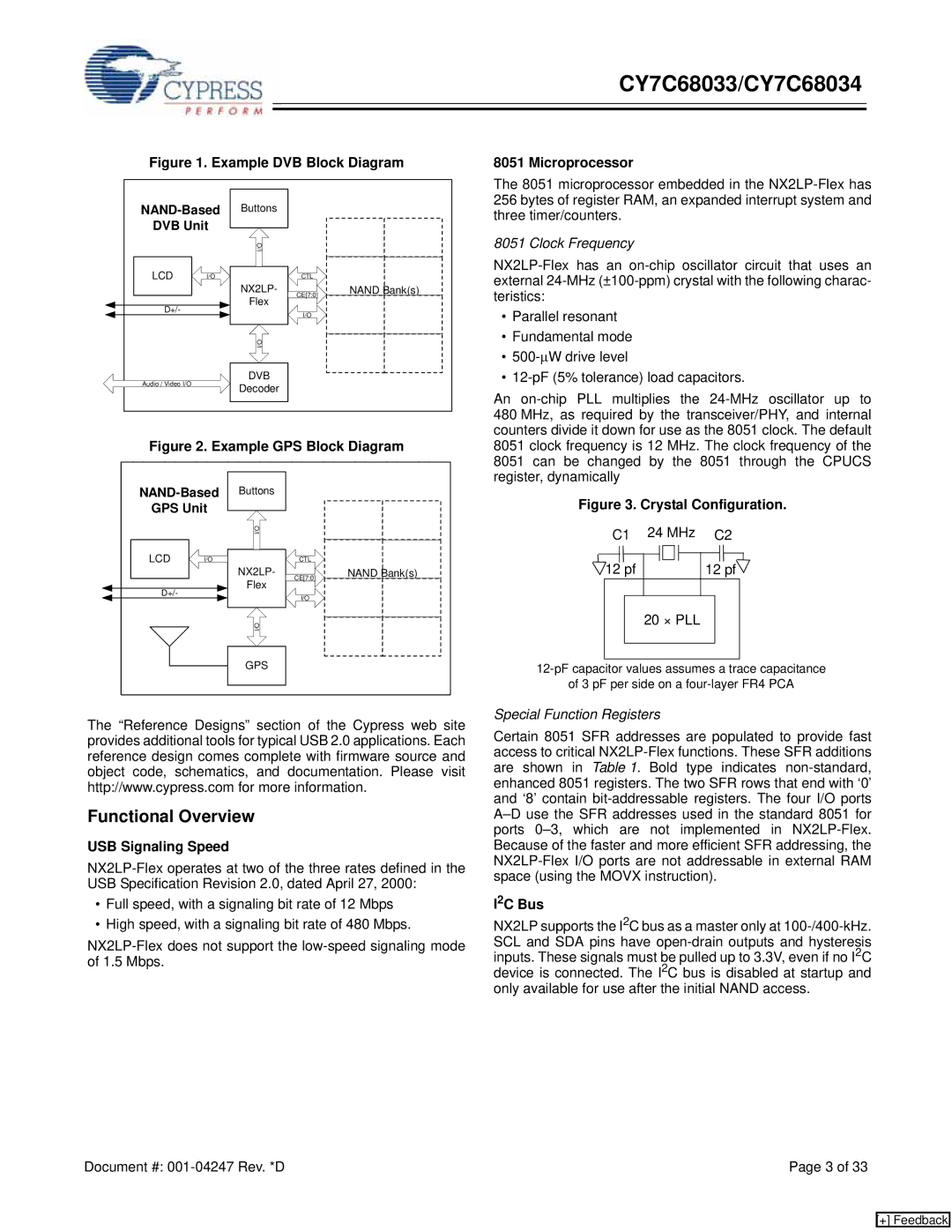

Figure 1. Example DVB Block Diagram

8051 Microprocessor

DVB Unit

LCD | I/O |

D+/-

Audio / Video I/O

Buttons

I/O

NX2LP-

Flex

I/O

DVB

Decoder

CTL |

|

CE[7:0] | NAND Bank(s) |

I/O |

|

The 8051 microprocessor embedded in the

8051 Clock Frequency

•Parallel resonant

•Fundamental mode

•

•

An

Figure 2. Example GPS Block Diagram

8051 clock frequency is 12 MHz. The clock frequency of the 8051 can be changed by the 8051 through the CPUCS register, dynamically

GPS Unit

LCD | I/O |

D+/-

Buttons

I/O

NX2LP-

Flex

I/O

GPS

CTL |

|

CE[7:0] | NAND Bank(s) |

I/O |

|

Figure 3. Crystal Configuration.

C1 24 MHz C2

|

|

|

|

|

|

|

|

|

|

|

|

| 12 |

| pf |

|

|

| 12 |

| pf |

| |

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

20 × PLL

of 3 pF per side on a

The “Reference Designs” section of the Cypress web site provides additional tools for typical USB 2.0 applications. Each reference design comes complete with firmware source and object code, schematics, and documentation. Please visit http://www.cypress.com for more information.

Functional Overview

USB Signaling Speed

•Full speed, with a signaling bit rate of 12 Mbps

•High speed, with a signaling bit rate of 480 Mbps.

Document #:

Special Function Registers

Certain 8051 SFR addresses are populated to provide fast access to critical

I2C Bus

NX2LP supports the I2C bus as a master only at

Page 3 of 33

[+] Feedback