CY7C68033/CY7C68034

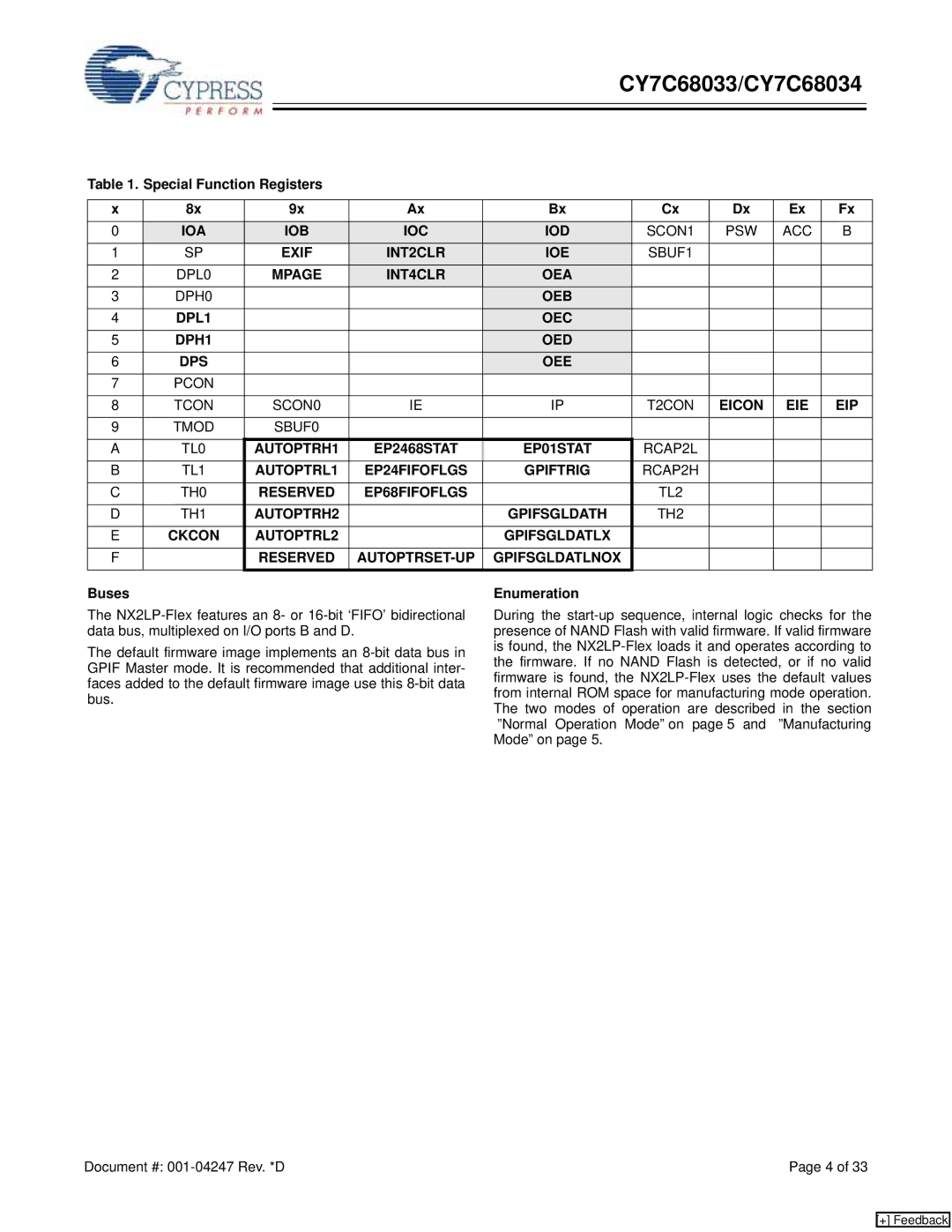

Table 1. Special Function Registers

x | 8x | 9x | Ax | Bx | Cx | Dx | Ex | Fx |

0 | IOA | IOB | IOC | IOD | SCON1 | PSW | ACC | B |

1 | SP | EXIF | INT2CLR | IOE | SBUF1 |

|

|

|

2 | DPL0 | MPAGE | INT4CLR | OEA |

|

|

|

|

3 | DPH0 |

|

| OEB |

|

|

|

|

4 | DPL1 |

|

| OEC |

|

|

|

|

5 | DPH1 |

|

| OED |

|

|

|

|

6 | DPS |

|

| OEE |

|

|

|

|

7 | PCON |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

8 | TCON | SCON0 | IE | IP | T2CON | EICON | EIE | EIP |

|

|

|

|

|

|

|

|

|

9 | TMOD | SBUF0 |

|

|

|

|

|

|

A | TL0 | AUTOPTRH1 | EP2468STAT | EP01STAT | RCAP2L |

|

|

|

B | TL1 | AUTOPTRL1 | EP24FIFOFLGS | GPIFTRIG | RCAP2H |

|

|

|

|

|

|

|

|

|

|

|

|

C | TH0 | RESERVED | EP68FIFOFLGS |

| TL2 |

|

|

|

D | TH1 | AUTOPTRH2 |

| GPIFSGLDATH | TH2 |

|

|

|

|

|

|

|

|

|

|

|

|

E | CKCON | AUTOPTRL2 |

| GPIFSGLDATLX |

|

|

|

|

|

|

|

|

|

|

|

|

|

F |

| RESERVED | GPIFSGLDATLNOX |

|

|

|

|

Buses

The

The default firmware image implements an

Enumeration

During the

Document #: | Page 4 of 33 |

[+] Feedback