|

|

|

|

|

|

|

| CY7C68033/CY7C68034 |

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

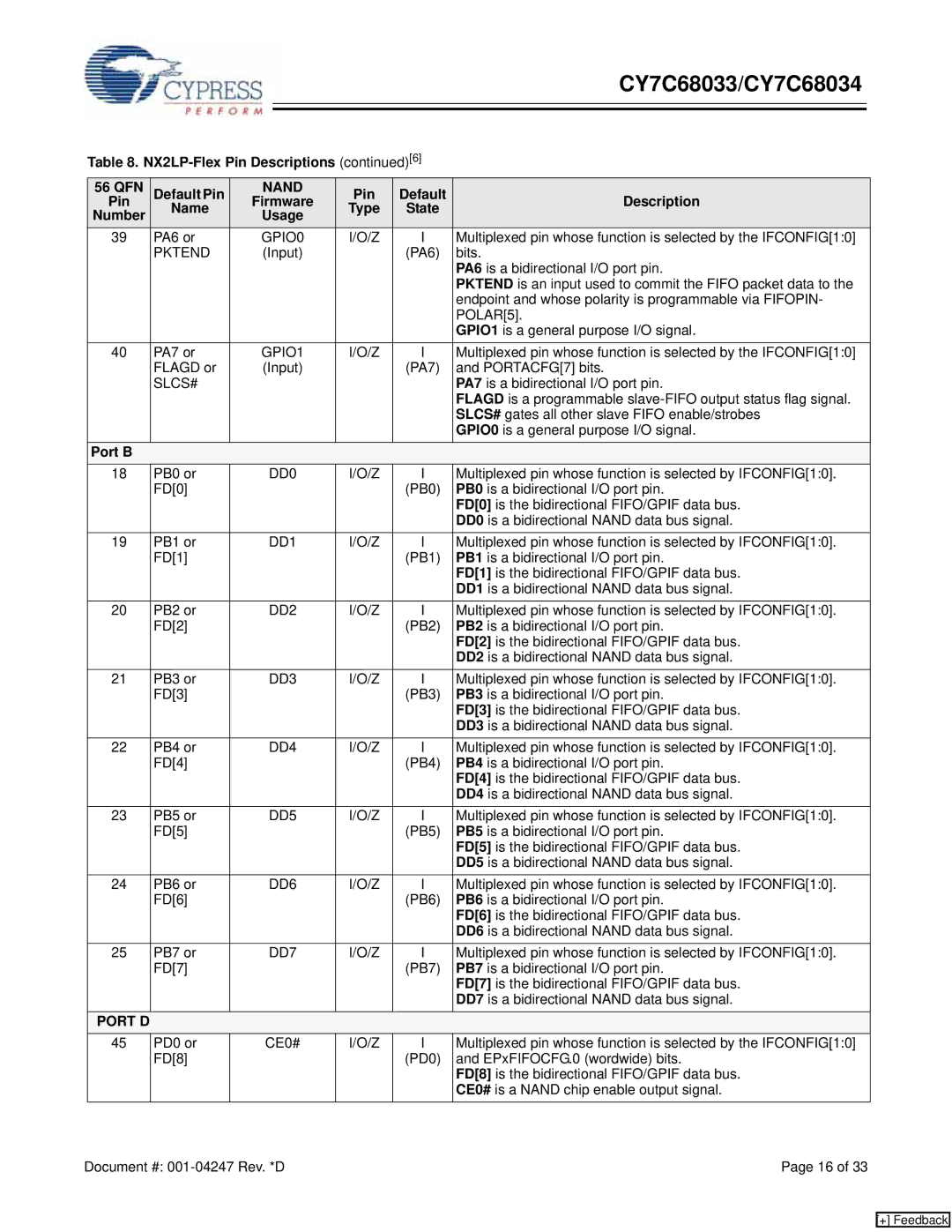

| Table 8. |

| ||||||

| 56 QFN | Default Pin | NAND | Pin | Default | Description | ||

| Pin | Name | Firmware | Type | State | |||

| Number | Usage |

| |||||

|

|

|

|

| ||||

| 39 | PA6 or | GPIO0 | I/O/Z | I | Multiplexed pin whose function is selected by the IFCONFIG[1:0] | ||

|

| PKTEND | (Input) |

| (PA6) | bits. | ||

|

|

|

|

|

|

|

| PA6 is a bidirectional I/O port pin. |

|

|

|

|

|

|

|

| PKTEND is an input used to commit the FIFO packet data to the |

|

|

|

|

|

|

|

| endpoint and whose polarity is programmable via FIFOPIN- |

|

|

|

|

|

|

|

| POLAR[5]. |

|

|

|

|

|

|

|

| GPIO1 is a general purpose I/O signal. |

| 40 | PA7 or | GPIO1 | I/O/Z | I | Multiplexed pin whose function is selected by the IFCONFIG[1:0] | ||

|

| FLAGD or | (Input) |

| (PA7) | and PORTACFG[7] bits. | ||

|

| SLCS# |

|

|

|

|

| PA7 is a bidirectional I/O port pin. |

|

|

|

|

|

|

|

| FLAGD is a programmable |

|

|

|

|

|

|

|

| SLCS# gates all other slave FIFO enable/strobes |

|

|

|

|

|

|

|

| GPIO0 is a general purpose I/O signal. |

| Port B |

|

|

|

|

|

|

|

| 18 | PB0 or |

| DD0 | I/O/Z | I | Multiplexed pin whose function is selected by IFCONFIG[1:0]. | |

|

| FD[0] |

|

|

|

| (PB0) | PB0 is a bidirectional I/O port pin. |

|

|

|

|

|

|

|

| FD[0] is the bidirectional FIFO/GPIF data bus. |

|

|

|

|

|

|

|

| DD0 is a bidirectional NAND data bus signal. |

| 19 | PB1 or |

| DD1 | I/O/Z | I | Multiplexed pin whose function is selected by IFCONFIG[1:0]. | |

|

| FD[1] |

|

|

|

| (PB1) | PB1 is a bidirectional I/O port pin. |

|

|

|

|

|

|

|

| FD[1] is the bidirectional FIFO/GPIF data bus. |

|

|

|

|

|

|

|

| DD1 is a bidirectional NAND data bus signal. |

| 20 | PB2 or |

| DD2 | I/O/Z | I | Multiplexed pin whose function is selected by IFCONFIG[1:0]. | |

|

| FD[2] |

|

|

|

| (PB2) | PB2 is a bidirectional I/O port pin. |

|

|

|

|

|

|

|

| FD[2] is the bidirectional FIFO/GPIF data bus. |

|

|

|

|

|

|

|

| DD2 is a bidirectional NAND data bus signal. |

| 21 | PB3 or |

| DD3 | I/O/Z | I | Multiplexed pin whose function is selected by IFCONFIG[1:0]. | |

|

| FD[3] |

|

|

|

| (PB3) | PB3 is a bidirectional I/O port pin. |

|

|

|

|

|

|

|

| FD[3] is the bidirectional FIFO/GPIF data bus. |

|

|

|

|

|

|

|

| DD3 is a bidirectional NAND data bus signal. |

| 22 | PB4 or |

| DD4 | I/O/Z | I | Multiplexed pin whose function is selected by IFCONFIG[1:0]. | |

|

| FD[4] |

|

|

|

| (PB4) | PB4 is a bidirectional I/O port pin. |

|

|

|

|

|

|

|

| FD[4] is the bidirectional FIFO/GPIF data bus. |

|

|

|

|

|

|

|

| DD4 is a bidirectional NAND data bus signal. |

| 23 | PB5 or |

| DD5 | I/O/Z | I | Multiplexed pin whose function is selected by IFCONFIG[1:0]. | |

|

| FD[5] |

|

|

|

| (PB5) | PB5 is a bidirectional I/O port pin. |

|

|

|

|

|

|

|

| FD[5] is the bidirectional FIFO/GPIF data bus. |

|

|

|

|

|

|

|

| DD5 is a bidirectional NAND data bus signal. |

| 24 | PB6 or |

| DD6 | I/O/Z | I | Multiplexed pin whose function is selected by IFCONFIG[1:0]. | |

|

| FD[6] |

|

|

|

| (PB6) | PB6 is a bidirectional I/O port pin. |

|

|

|

|

|

|

|

| FD[6] is the bidirectional FIFO/GPIF data bus. |

|

|

|

|

|

|

|

| DD6 is a bidirectional NAND data bus signal. |

| 25 | PB7 or |

| DD7 | I/O/Z | I | Multiplexed pin whose function is selected by IFCONFIG[1:0]. | |

|

| FD[7] |

|

|

|

| (PB7) | PB7 is a bidirectional I/O port pin. |

|

|

|

|

|

|

|

| FD[7] is the bidirectional FIFO/GPIF data bus. |

|

|

|

|

|

|

|

| DD7 is a bidirectional NAND data bus signal. |

| PORT D |

|

|

|

|

|

|

|

| 45 | PD0 or |

| CE0# | I/O/Z | I | Multiplexed pin whose function is selected by the IFCONFIG[1:0] | |

|

| FD[8] |

|

|

|

| (PD0) | and EPxFIFOCFG.0 (wordwide) bits. |

|

|

|

|

|

|

|

| FD[8] is the bidirectional FIFO/GPIF data bus. |

|

|

|

|

|

|

|

| CE0# is a NAND chip enable output signal. |

Document #: |

|

| Page 16 of 33 | |||||

[+] Feedback