CY7C68053 specifications

The Cypress CY7C68053 is a versatile USB microcontroller known for its strong performance and rich feature set, catering to a wide range of applications requiring USB connectivity. Part of the Cypress family of USB products, this microcontroller combines the convenience of USB interfacing with powerful embedded processing capabilities.At its core, the CY7C68053 is built on an 8051 microcontroller architecture, enabling efficient data handling and control operations. It operates at speeds of up to 48 MHz, providing ample processing power for complex applications. The device features an integrated USB 2.0 full-speed controller, which allows for high-speed data transfer rates of up to 12 Mbps. This makes it ideal for applications such as data transfer, communication devices, and real-time processing tasks.

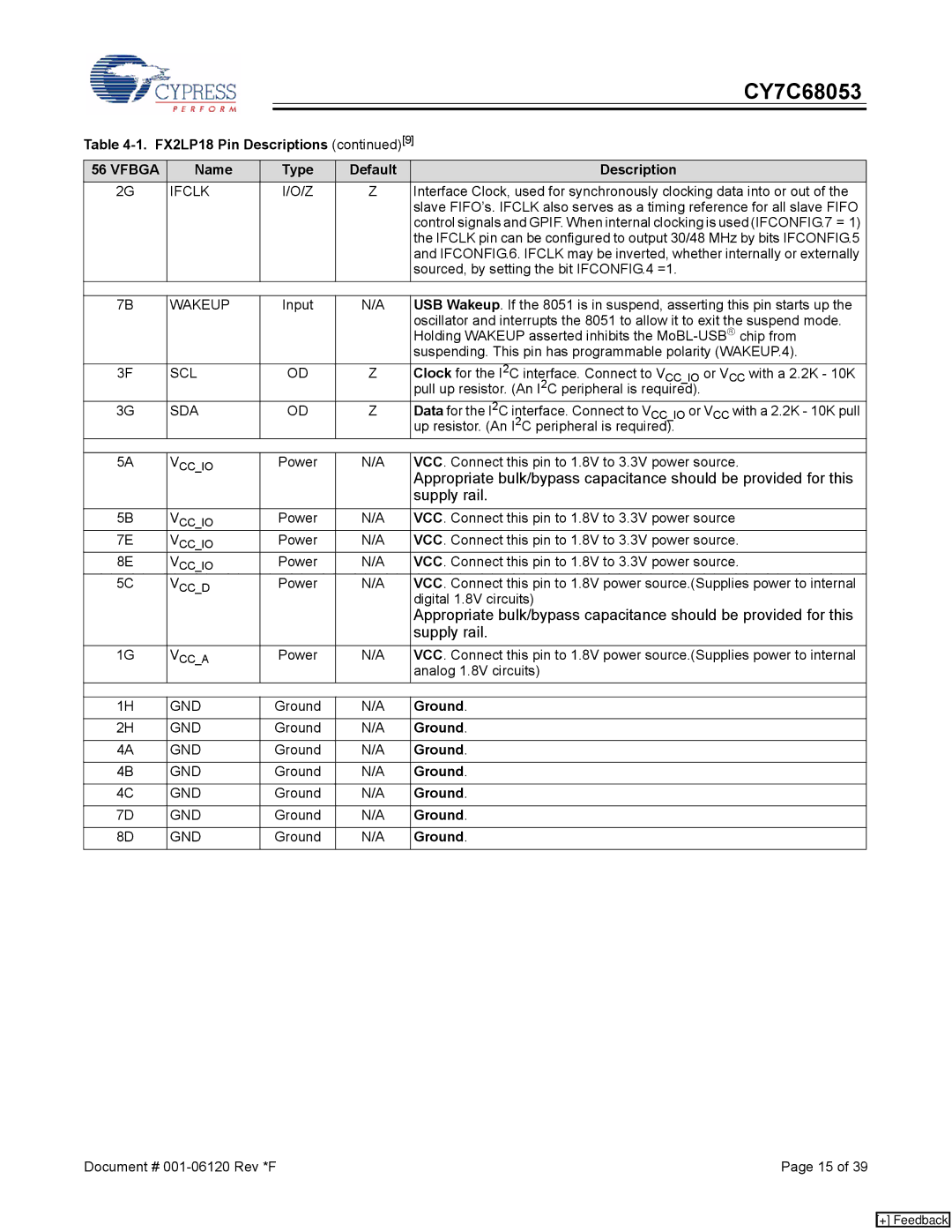

One of the standout features of the CY7C68053 is its flexible pin configuration. It supports a variety of operating modes, including peripheral mode, host mode, and a combination of both, allowing it to cater to diverse application requirements. Additionally, the device offers a large number of GPIO pins that can be used for various control and communication tasks. This flexibility ensures that developers can tailor the hardware to meet the specific needs of their application.

In terms of development, the CY7C68053 is backed by a robust set of software development tools from Cypress. The EZ-USB development kit provides a comprehensive platform for firmware development, testing, and debugging. This kit includes libraries, example projects, and a user-friendly integrated development environment (IDE), streamlining the development process for engineers.

The CY7C68053 is also equipped with an extensive memory system, featuring 32 kB of in-system programmable Flash memory, 2 kB of SRAM, and 128 bytes of EEPROM. This memory capacity allows for the storage of complex firmware and user data, enhancing the device's versatility.

Moreover, the CY7C68053 is designed with low power consumption in mind. It includes power management features that allow it to operate efficiently, making it suitable for battery-operated devices.

In summary, the Cypress CY7C68053 stands out as a powerful USB microcontroller that combines high-speed processing, flexible configurations, and robust software support. Its features make it an excellent choice for developers looking to create innovative USB-enabled products across various applications.