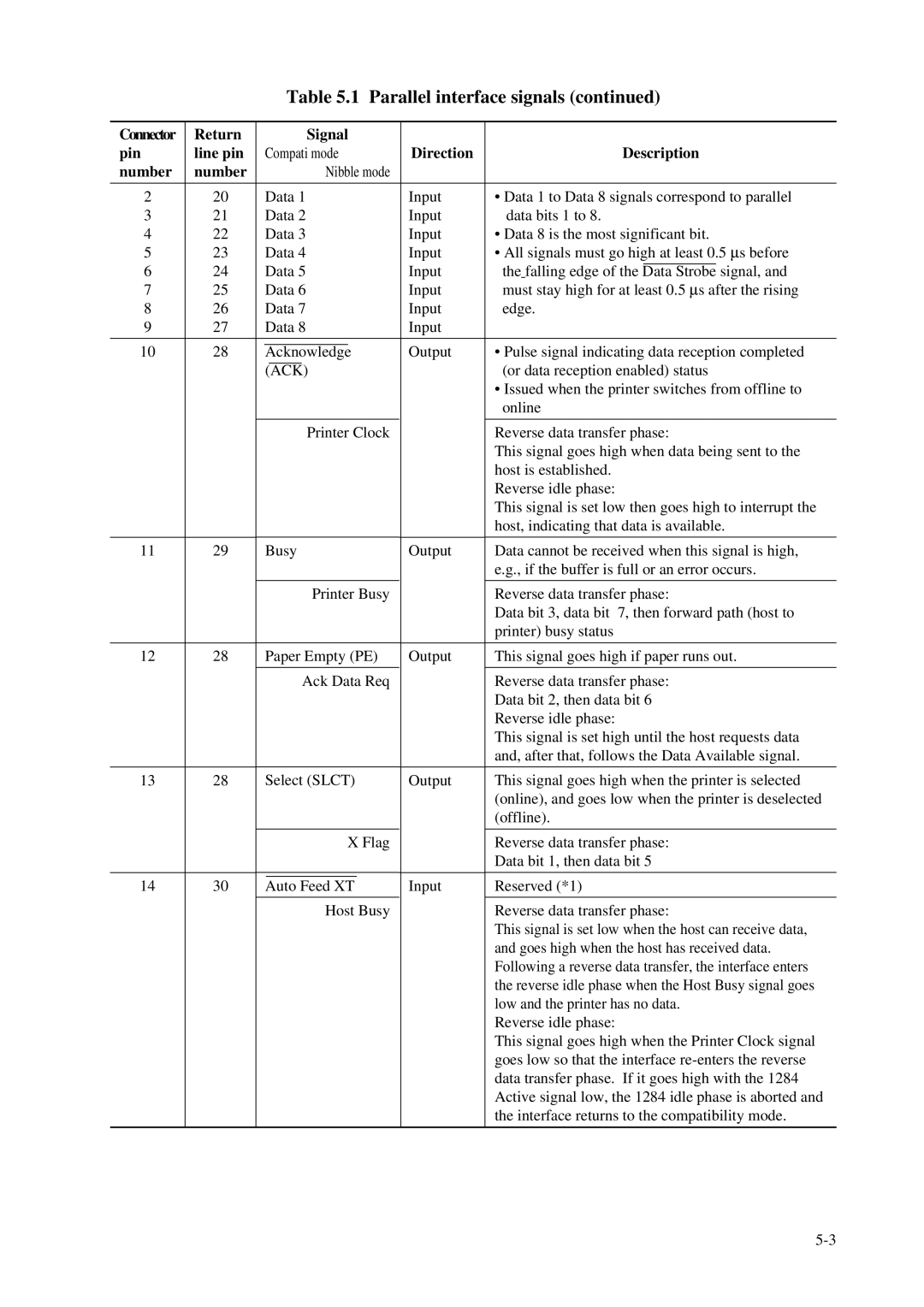

Table 5.1 Parallel interface signals (continued)

Connector | Return |

|

|

|

| Signal |

|

|

|

| ||

pin | line pin |

| Compati mode | Direction | Description | |||||||

number | number |

|

|

|

| Nibble mode |

|

|

|

| ||

|

|

|

|

|

|

|

| |||||

2 | 20 |

| Data 1 | Input | • Data 1 to Data 8 signals correspond to parallel | |||||||

3 | 21 |

| Data 2 | Input | data bits 1 to 8. | |||||||

4 | 22 |

| Data 3 | Input | • Data 8 is the most significant bit. | |||||||

5 | 23 |

| Data 4 | Input | • All signals must go high at least 0.5 μs before | |||||||

6 | 24 |

| Data 5 | Input | the falling edge of the |

| signal, and | |||||

| Data Strobe | |||||||||||

7 | 25 |

| Data 6 | Input | must stay high for at least 0.5 μs after the rising | |||||||

8 | 26 |

| Data 7 | Input | edge. | |||||||

9 | 27 |

| Data 8 | Input |

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

| ||

10 | 28 |

|

|

|

|

|

|

| Output | • Pulse signal indicating data reception completed | ||

Acknowledge | ||||||||||||

|

|

|

|

|

|

|

|

| (or data reception enabled) status | |||

|

|

| (ACK) |

| ||||||||

|

|

|

|

|

|

|

|

|

| • Issued when the printer switches from offline to | ||

|

|

|

|

|

|

|

|

|

| online | ||

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

| Printer Clock |

| Reverse data transfer phase: | ||||

|

|

|

|

|

|

|

|

|

| This signal goes high when data being sent to the | ||

|

|

|

|

|

|

|

|

|

| host is established. | ||

|

|

|

|

|

|

|

|

|

| Reverse idle phase: | ||

|

|

|

|

|

|

|

|

|

| This signal is set low then goes high to interrupt the | ||

|

|

|

|

|

|

|

|

|

| host, indicating that data is available. | ||

|

|

|

|

|

|

|

| |||||

11 | 29 |

| Busy | Output | Data cannot be received when this signal is high, | |||||||

|

|

|

|

|

|

|

|

|

| e.g., if the buffer is full or an error occurs. | ||

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

| Printer Busy |

| Reverse data transfer phase: | ||||

|

|

|

|

|

|

|

|

|

| Data bit 3, data bit 7, then forward path (host to | ||

|

|

|

|

|

|

|

|

|

| printer) busy status | ||

|

|

|

|

|

|

|

| |||||

12 | 28 |

| Paper Empty (PE) | Output | This signal goes high if paper runs out. | |||||||

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

| Ack Data Req |

| Reverse data transfer phase: | ||||

|

|

|

|

|

|

|

|

|

| Data bit 2, then data bit 6 | ||

|

|

|

|

|

|

|

|

|

| Reverse idle phase: | ||

|

|

|

|

|

|

|

|

|

| This signal is set high until the host requests data | ||

|

|

|

|

|

|

|

|

|

| and, after that, follows the Data Available signal. | ||

|

|

|

|

|

|

|

| |||||

13 | 28 |

| Select (SLCT) | Output | This signal goes high when the printer is selected | |||||||

|

|

|

|

|

|

|

|

|

| (online), and goes low when the printer is deselected | ||

|

|

|

|

|

|

|

|

|

| (offline). | ||

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

| X Flag |

| Reverse data transfer phase: | ||||

|

|

|

|

|

|

|

|

|

| Data bit 1, then data bit 5 | ||

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

| |||||

14 | 30 |

| Auto Feed XT | Input | Reserved (*1) | |||||||

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

| Host Busy |

| Reverse data transfer phase: | ||||

|

|

|

|

|

|

|

|

|

| This signal is set low when the host can receive data, | ||

|

|

|

|

|

|

|

|

|

| and goes high when the host has received data. | ||

|

|

|

|

|

|

|

|

|

| Following a reverse data transfer, the interface enters | ||

|

|

|

|

|

|

|

|

|

| the reverse idle phase when the Host Busy signal goes | ||

|

|

|

|

|

|

|

|

|

| low and the printer has no data. | ||

|

|

|

|

|

|

|

|

|

| Reverse idle phase: | ||

|

|

|

|

|

|

|

|

|

| This signal goes high when the Printer Clock signal | ||

|

|

|

|

|

|

|

|

|

| goes low so that the interface | ||

|

|

|

|

|

|

|

|

|

| data transfer phase. If it goes high with the 1284 | ||

|

|

|

|

|

|

|

|

|

| Active signal low, the 1284 idle phase is aborted and | ||

|

|

|

|

|

|

|

|

|

| the interface returns to the compatibility mode. | ||

|

|

|

|

|

|

|

|

|

|

|

|

|