4.2Interrupt Control

4.2.1System Architecture

The

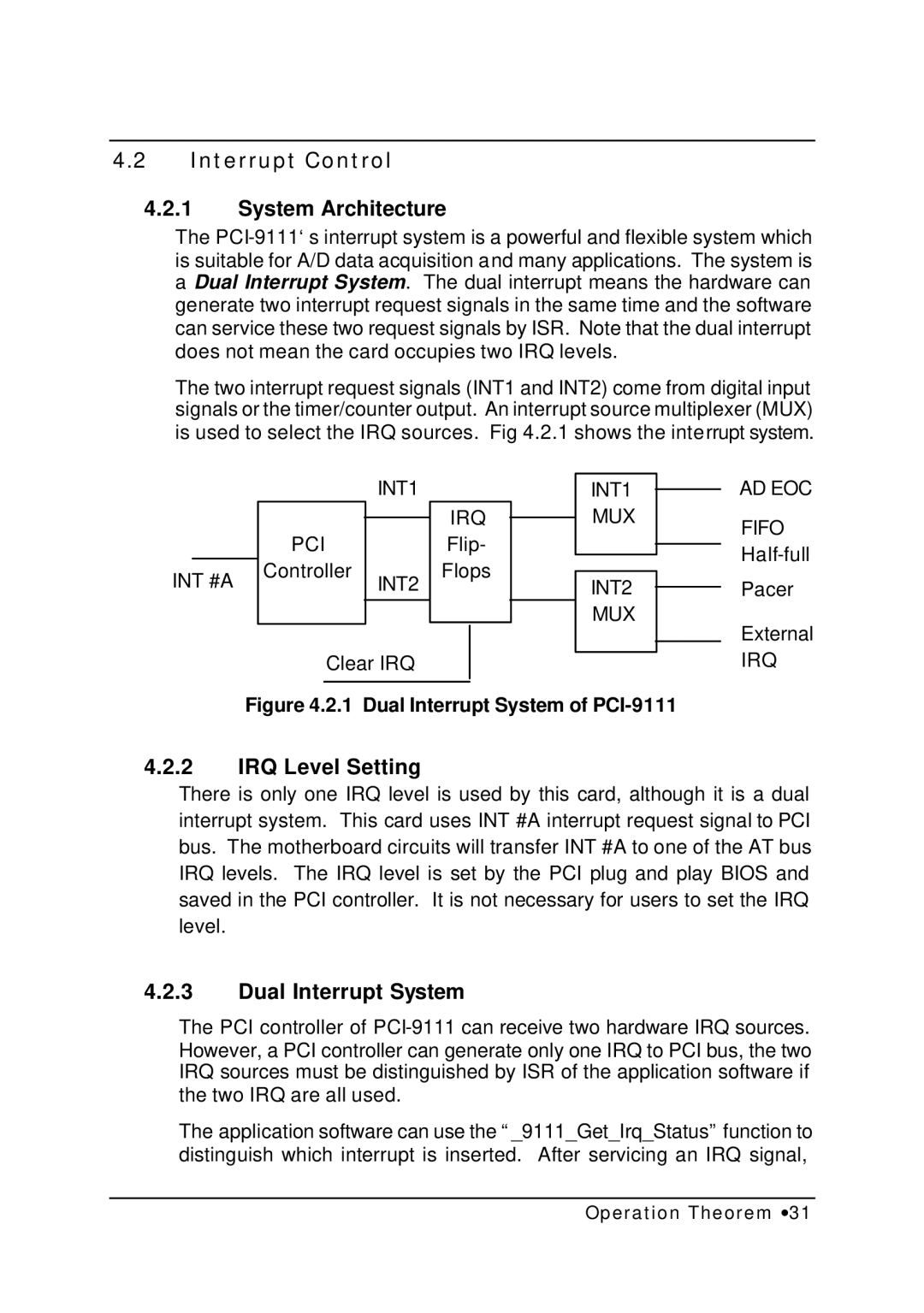

The two interrupt request signals (INT1 and INT2) come from digital input signals or the timer/counter output. An interrupt source multiplexer (MUX) is used to select the IRQ sources. Fig 4.2.1 shows the interrupt system.

|

|

|

|

| INT1 |

|

|

|

| INT1 |

|

| AD EOC |

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

| IRQ |

|

| MUX |

| FIFO | ||

|

|

|

|

|

|

|

|

| |||||

|

| PCI |

| Flip- |

|

|

|

| |||||

|

|

|

|

|

|

| |||||||

|

|

|

|

|

|

| |||||||

|

| Controller |

| Flops |

|

|

|

| |||||

INT #A | INT2 |

|

|

| |||||||||

|

|

|

|

| |||||||||

| INT2 |

|

| Pacer | |||||||||

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

| MUX |

| External | |

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

| Clear IRQ |

|

|

|

|

|

|

| IRQ | ||

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Figure 4.2.1 Dual Interrupt System of PCI-9111

4.2.2IRQ Level Setting

There is only one IRQ level is used by this card, although it is a dual interrupt system. This card uses INT #A interrupt request signal to PCI bus. The motherboard circuits will transfer INT #A to one of the AT bus IRQ levels. The IRQ level is set by the PCI plug and play BIOS and saved in the PCI controller. It is not necessary for users to set the IRQ level.

4.2.3Dual Interrupt System

The PCI controller of

The application software can use the “_9111_Get_Irq_Status” function to distinguish which interrupt is inserted. After servicing an IRQ signal,

Operation Theorem ∙31