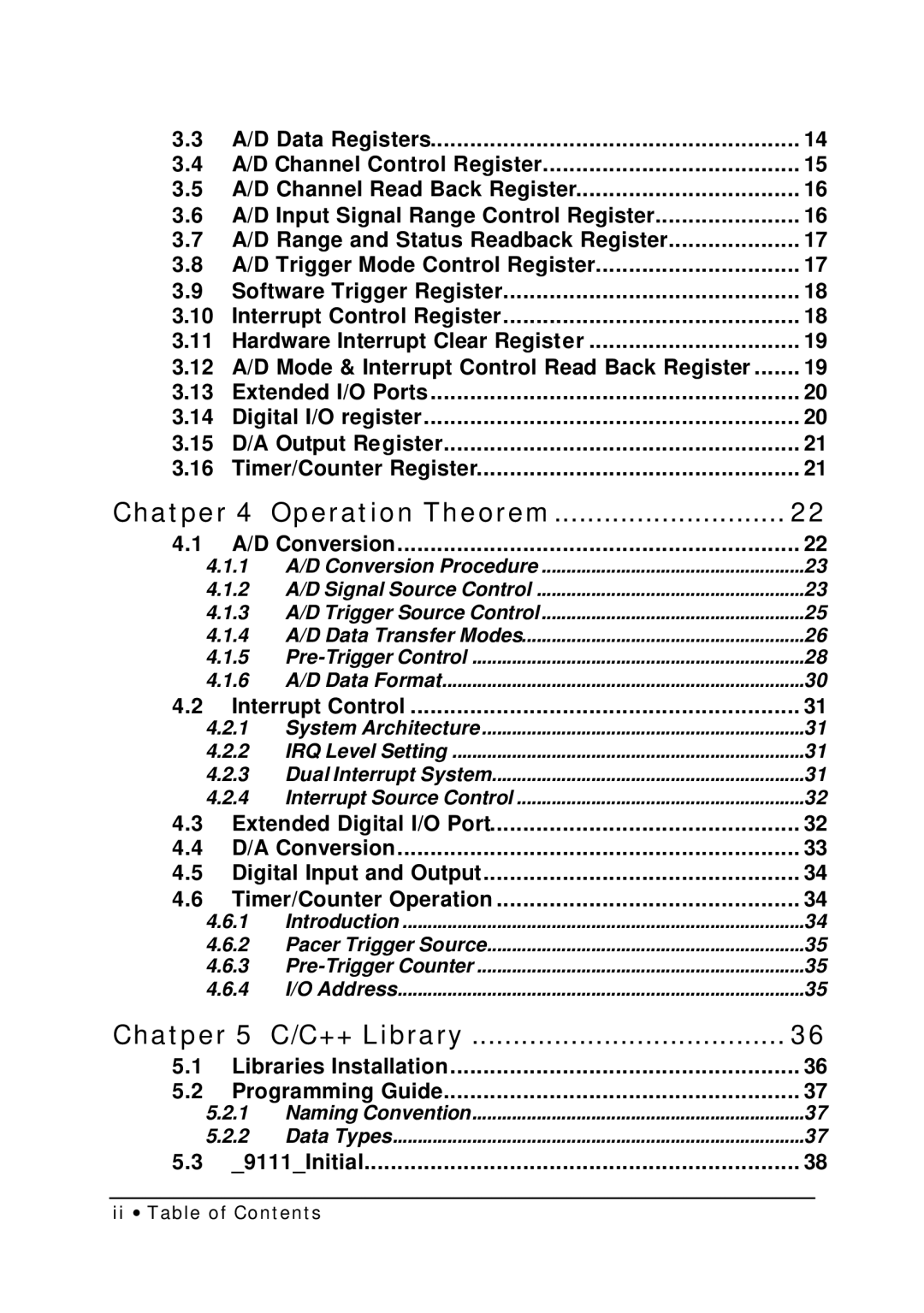

3.3 | A/D Data Registers | 14 |

3.4 | A/D Channel Control Register | 15 |

3.5 | A/D Channel Read Back Register | 16 |

3.6 | A/D Input Signal Range Control Register | 16 |

3.7 | A/D Range and Status Readback Register | 17 |

3.8 | A/D Trigger Mode Control Register | 17 |

3.9 | Software Trigger Register | 18 |

3.10 | Interrupt Control Register | 18 |

3.11 | Hardware Interrupt Clear Register | 19 |

3.12 | A/D Mode & Interrupt Control Read Back Register | 19 |

3.13 | Extended I/O Ports | 20 |

3.14 | Digital I/O register | 20 |

3.15 | D/A Output Register | 21 |

3.16 | Timer/Counter Register | 21 |

Chatper 4 Operation Theorem | 22 | ||

4.1 | A/D Conversion | 22 | |

| 4.1.1 | A/D Conversion Procedure | 23 |

| 4.1.2 | A/D Signal Source Control | 23 |

| 4.1.3 | A/D Trigger Source Control | 25 |

| 4.1.4 | A/D Data Transfer Modes | 26 |

| 4.1.5 | 28 | |

| 4.1.6 | A/D Data Format | 30 |

4.2 | Interrupt Control | 31 | |

| 4.2.1 | System Architecture | 31 |

| 4.2.2 | IRQ Level Setting | 31 |

| 4.2.3 | Dual Interrupt System | 31 |

| 4.2.4 | Interrupt Source Control | 32 |

4.3 | Extended Digital I/O Port | 32 | |

4.4 | D/A Conversion | 33 | |

4.5 | Digital Input and Output | 34 | |

4.6 | Timer/Counter Operation | 34 | |

| 4.6.1 | Introduction | 34 |

| 4.6.2 | Pacer Trigger Source | 35 |

| 4.6.3 | 35 | |

| 4.6.4 | I/O Address | 35 |

Chatper 5 C/C++ Library | 36 | ||

5.1 | Libraries Installation | 36 | |

5.2 | Programming Guide | 37 | |

| 5.2.1 | Naming Convention | 37 |

| 5.2.2 | Data Types | 37 |

5.3 | _9111_Initial | 38 | |