software must continuously read data out from the FIFO to prevent FIFO full. The software also should poll the counter value to check if the A/D sampling is stopped.

To set up the

1.Set

2.Set 8254 Counter #0 value N (N=1~65535). Note that the larger the counter value, the more host memory buffer is needed.

3.Set up A/D data acquire, including, A/D range, channel scan, data transfer mode and so on.

4.Set

5.Read A/D data into host PC memory buffer by certain data transfer method, otherwise the FIFO will full. At the same time, wait the

6.If A/D is stopped, set the

7.Go to Step 1 to set the

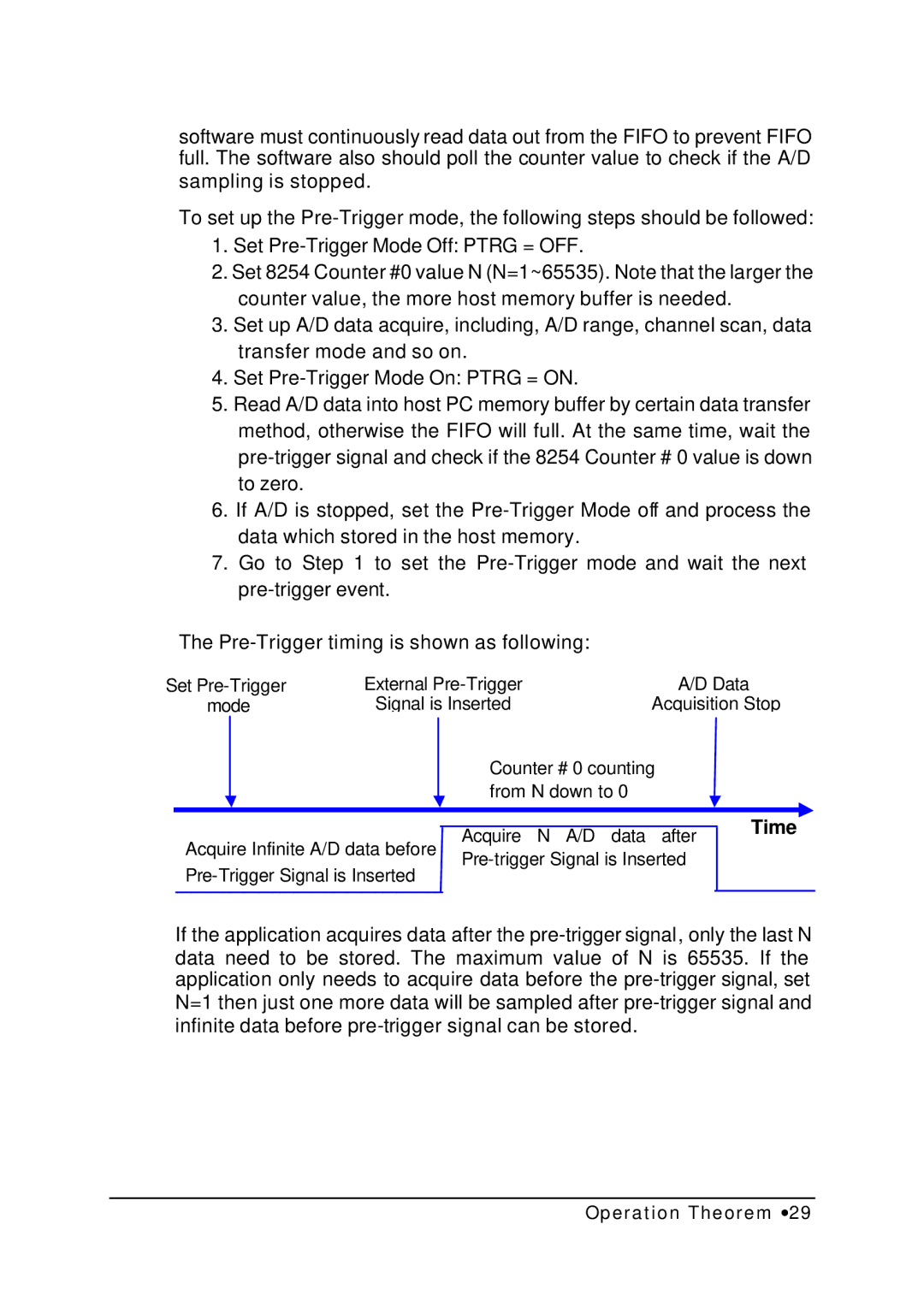

The

Set | External | A/D Data |

|

| ||||||

| mode | Signal is Inserted | Acquisition Stop |

| ||||||

|

|

|

|

| Counter # 0 counting |

|

| |||

|

|

|

|

| from N down to 0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Time |

|

| Acquire Infinite A/D data before |

| Acquire N A/D data after |

|

| |||||

|

|

|

|

| ||||||

|

|

|

|

| ||||||

|

|

|

|

| ||||||

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

If the application acquires data after the

Operation Theorem ∙29