BIOS Quick Reference

A complete discussion of the debugger is beyond the scope of this chapter; however, complete documentation is available from General Software via the web at http://www.gensw.com.

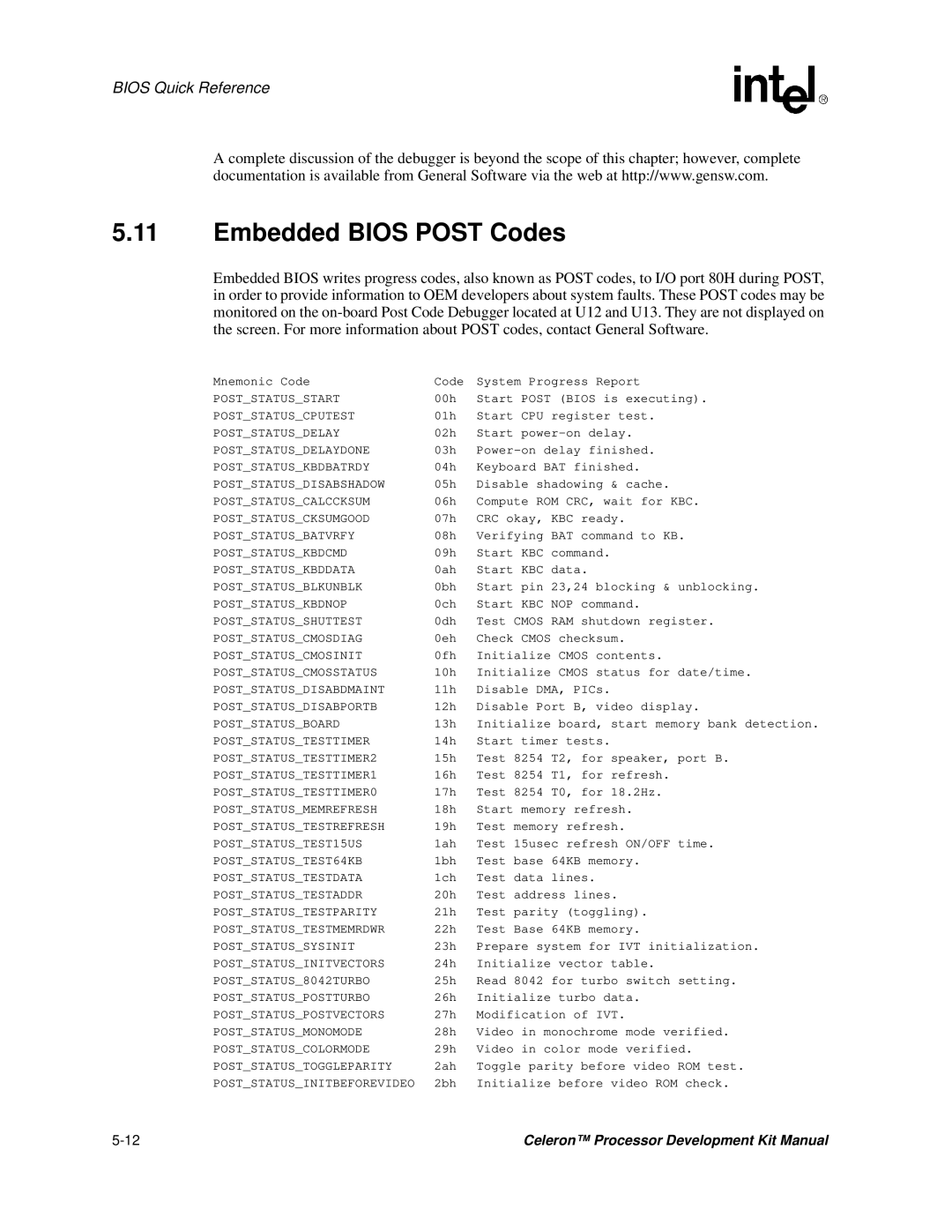

5.11Embedded BIOS POST Codes

Embedded BIOS writes progress codes, also known as POST codes, to I/O port 80H during POST, in order to provide information to OEM developers about system faults. These POST codes may be monitored on the

Mnemonic Code | Code | System Progress Report | |

POST_STATUS_START | 00h | Start POST (BIOS is executing). | |

POST_STATUS_CPUTEST | 01h | Start CPU | register test. |

POST_STATUS_DELAY | 02h | Start | |

POST_STATUS_DELAYDONE | 03h | ||

POST_STATUS_KBDBATRDY | 04h | Keyboard BAT finished. | |

POST_STATUS_DISABSHADOW | 05h | Disable shadowing & cache. | |

POST_STATUS_CALCCKSUM | 06h | Compute ROM CRC, wait for KBC. | |

POST_STATUS_CKSUMGOOD | 07h | CRC okay, | KBC ready. |

POST_STATUS_BATVRFY | 08h | Verifying | BAT command to KB. |

POST_STATUS_KBDCMD | 09h | Start KBC | command. |

POST_STATUS_KBDDATA | 0ah | Start KBC | data. |

POST_STATUS_BLKUNBLK | 0bh | Start pin | 23,24 blocking & unblocking. |

POST_STATUS_KBDNOP | 0ch | Start KBC | NOP command. |

POST_STATUS_SHUTTEST | 0dh | Test CMOS | RAM shutdown register. |

POST_STATUS_CMOSDIAG | 0eh | Check CMOS checksum. | |

POST_STATUS_CMOSINIT | 0fh | Initialize CMOS contents. | |

POST_STATUS_CMOSSTATUS | 10h | Initialize CMOS status for date/time. | |

POST_STATUS_DISABDMAINT | 11h | Disable DMA, PICs. | |

POST_STATUS_DISABPORTB | 12h | Disable Port B, video display. | |

POST_STATUS_BOARD | 13h | Initialize board, start memory bank detection. | |

POST_STATUS_TESTTIMER | 14h | Start timer tests. | |

POST_STATUS_TESTTIMER2 | 15h | Test 8254 | T2, for speaker, port B. |

POST_STATUS_TESTTIMER1 | 16h | Test 8254 | T1, for refresh. |

POST_STATUS_TESTTIMER0 | 17h | Test 8254 | T0, for 18.2Hz. |

POST_STATUS_MEMREFRESH | 18h | Start memory refresh. | |

POST_STATUS_TESTREFRESH | 19h | Test memory refresh. | |

POST_STATUS_TEST15US | 1ah | Test 15usec refresh ON/OFF time. | |

POST_STATUS_TEST64KB | 1bh | Test base | 64KB memory. |

POST_STATUS_TESTDATA | 1ch | Test data | lines. |

POST_STATUS_TESTADDR | 20h | Test address lines. | |

POST_STATUS_TESTPARITY | 21h | Test parity (toggling). | |

POST_STATUS_TESTMEMRDWR | 22h | Test Base | 64KB memory. |

POST_STATUS_SYSINIT | 23h | Prepare system for IVT initialization. | |

POST_STATUS_INITVECTORS | 24h | Initialize vector table. | |

POST_STATUS_8042TURBO | 25h | Read 8042 | for turbo switch setting. |

POST_STATUS_POSTTURBO | 26h | Initialize turbo data. | |

POST_STATUS_POSTVECTORS | 27h | Modification of IVT. | |

POST_STATUS_MONOMODE | 28h | Video in monochrome mode verified. | |

POST_STATUS_COLORMODE | 29h | Video in color mode verified. | |

POST_STATUS_TOGGLEPARITY | 2ah | Toggle parity before video ROM test. | |

POST_STATUS_INITBEFOREVIDEO | 2bh | Initialize before video ROM check. | |

Celeron™ Processor Development Kit Manual |