| A | B | C | D | E |

|

V 5 _ 0

C 1 9 6 0 . 1uF

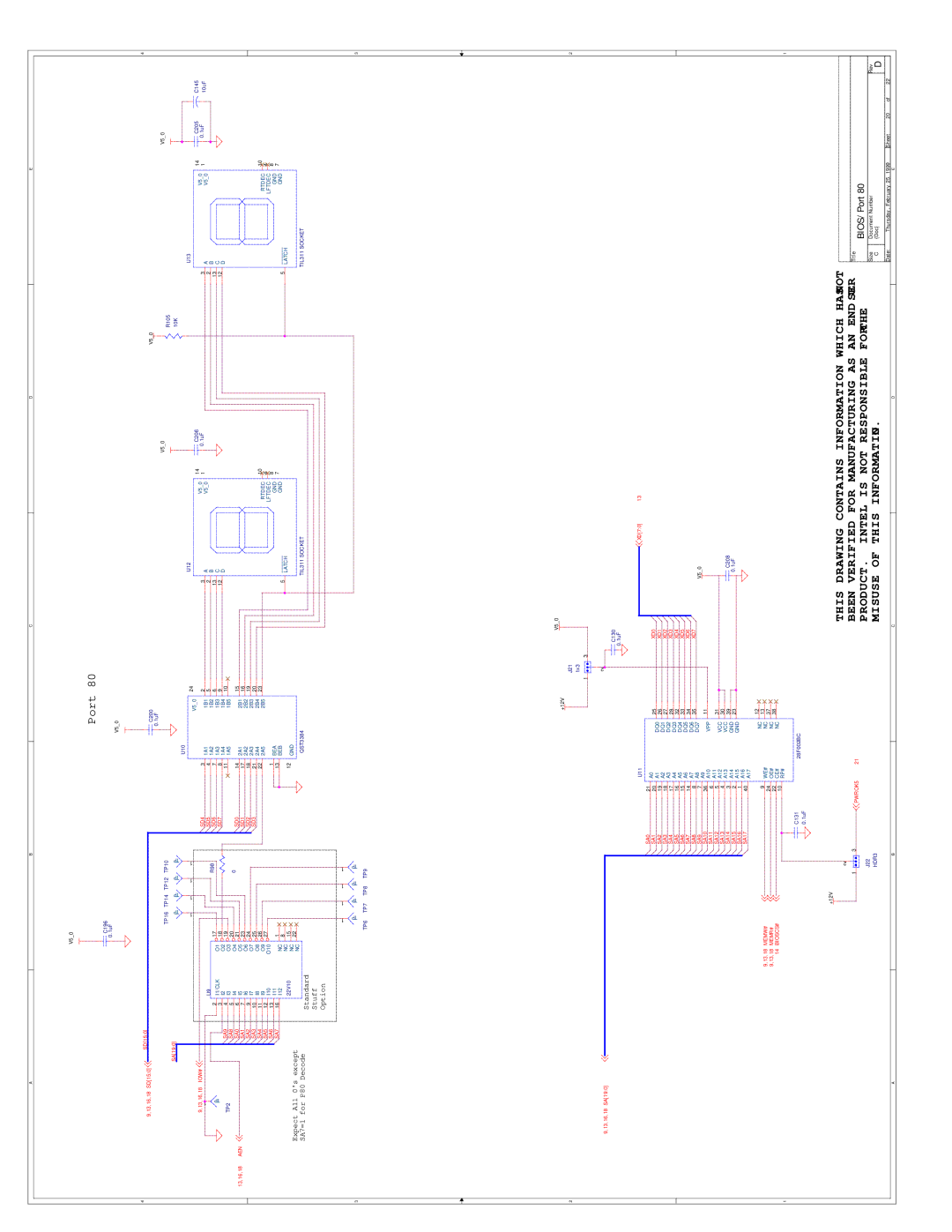

Port 80

4

9,13,16,18 SD[15:0] ![]()

SD[15:0]

V 5 _ 0 |

|

C 2 0 | 0 |

0 . 1uF |

|

V 5 _ 0

4

3

2

SA[19:0]

9,13,16,18 IOW#

1 |

|

|

| TP |

|

| T P 2 | SA9 |

|

| SA8 | |

|

|

| |

13,16,18 | AEN |

| SA0 |

| SA1 | ||

|

|

| SA2 |

|

|

| SA3 |

|

|

| SA4 |

|

|

| SA5 |

|

|

| SA6 |

|

|

| SA7 |

Expect All 0's except

SA7=1 for P80 Decode

|

|

| T P 1 6 T P 1 4 T P 1 2 T P 1 0 |

| |||

|

|

| TP | TP | TP | TP |

|

|

|

| 1 | 1 | 1 | 1 |

|

|

|

|

|

|

|

| SD4 |

| U9 |

|

|

|

| R98 | SD5 |

2 | I1/CLK | O 1 | 1 7 |

|

| SD6 | |

3 | 1 8 |

|

|

| SD7 | ||

I2 | O 2 |

|

|

| |||

4 | 1 9 |

|

|

|

| ||

I3 | O 3 |

|

|

|

| ||

5 | 2 0 |

|

| 0 |

| ||

I4 | O 4 |

|

| SD0 | |||

6 | 2 1 |

|

| ||||

I5 | O 5 |

|

|

| |||

7 | 2 3 |

|

|

| SD1 | ||

I6 | O 6 |

|

|

| |||

9 | 2 4 |

|

|

| SD2 | ||

I7 | O 7 |

|

|

| |||

1 0 | 2 5 |

|

|

| SD3 | ||

I8 | O 8 |

|

|

| |||

1 1 | 2 6 |

|

|

|

| ||

I9 | O 9 |

|

|

|

| ||

1 2 | 2 7 |

|

|

|

| ||

I10 | O 1 0 |

|

|

|

| ||

1 3 |

|

|

|

|

| ||

I11 |

|

|

|

|

|

| |

1 6 |

| 1 |

|

|

|

| |

I12 | NC |

|

|

|

| ||

| 8 |

|

|

|

| ||

|

| NC |

|

|

|

| |

| 2 2 V 1 0 | 1 5 |

|

|

|

| |

| NC |

|

|

|

| ||

|

| 2 2 |

|

|

|

| |

|

| NC |

|

|

|

| |

|

|

|

|

|

|

| |

Standard |

|

|

|

|

|

| |

Stuff |

|

|

|

|

|

| |

Option |

|

|

|

|

|

| |

|

|

| 1 | 1 | 1 | 1 |

|

|

|

| TP | TP | TP | TP |

|

|

|

| T P 6 T P 7 T P 8 T P 9 |

| |||

| U10 |

| |

|

| V 5 _ 0 | |

3 | 1 A 1 | 1 B 1 | |

4 | |||

1 A 2 | 1 B 2 | ||

7 | |||

1 A 3 | 1 B 3 | ||

8 | |||

1 A 4 | 1 B 4 | ||

1 1 | |||

1 A 5 | 1 B 5 | ||

| |||

1 4 | 2 A 1 | 2 B 1 | |

1 7 | |||

2 A 2 | 2 B 2 | ||

1 8 | |||

2 A 3 | 2 B 3 | ||

2 1 | |||

2 A 4 | 2 B 4 | ||

2 2 | |||

2 A 5 | 2 B 5 | ||

| |||

1 |

|

|

1 3 | BEA | |

BEB | ||

| ||

1 2 | GND | |

| ||

| Q S T 3 3 8 4 |

+ 1 2 V

2 4 |

| U12 | |

|

| ||

2 | 3 | A | |

5 | 2 | ||

B | |||

6 | 1 3 | ||

C | |||

9 | 1 2 | ||

D | |||

1 0 |

| ||

|

|

1 5

1 6

5 | LATCH |

|

T I L 3 1 1 S O C K E T

V 5 _ 0

J21

1x3

1 ![]() 3

3

|

| V 5 _ 0 |

|

| R 1 0 5 |

|

| 1 0 K |

V 5 _ 0 | 1 4 | C 2 0 6 |

1 | 0 . 1uF | |

V 5 _ 0 |

|

|

RTDEC | 1 0 |

|

4 |

| |

L F T D E C |

| |

8 |

| |

GND |

| |

7 |

| |

GND |

| |

|

|

U13

3 | A | |

2 | ||

B | ||

1 3 | ||

C | ||

1 2 | ||

D | ||

| ||

5 | LATCH | |

|

T I L 3 1 1 S O C K E T

|

| V 5 _ 0 |

|

V 5 _ 0 | 1 4 | C 2 0 5 | C 1 4 5 |

1 | 0 . 1uF | 1 0 u F | |

V 5 _ 0 |

| ||

|

|

| |

RTDEC | 1 0 |

|

|

4 |

|

| |

L F T D E C |

|

| |

8 |

|

| |

GND |

|

| |

7 |

|

| |

GND |

|

| |

|

|

|

3

2

1

9,13,16,18 SA[19:0]

9,13,18 M E M W #

9,13,18 M E M R #

1 4 BIOSCS#

|

| U11 |

| |

SA0 | 2 1 | A 0 |

| |

SA1 | 2 0 |

| ||

A 1 | D Q 0 | |||

SA2 | 1 9 | |||

A 2 | D Q 1 | |||

SA3 | 1 8 | |||

A 3 | D Q 2 | |||

SA4 | 1 7 | |||

A 4 | D Q 3 | |||

SA5 | 1 6 | |||

A 5 | D Q 4 | |||

SA6 | 1 5 | |||

A 6 | D Q 5 | |||

SA7 | 1 4 | |||

A 7 | D Q 6 | |||

SA8 | 8 | |||

A 8 | D Q 7 | |||

SA9 | 7 | |||

S A 1 0 | 3 6 | A 9 |

| |

A 1 0 | VPP | |||

S A 1 1 | 6 | |||

A 1 1 |

| |||

S A 1 2 | 5 |

| ||

A 1 2 | VCC | |||

S A 1 3 | 4 | |||

A 1 3 | VCC | |||

S A 1 4 | 3 | |||

A 1 4 | GND | |||

S A 1 5 | 2 | |||

A 1 5 | GND | |||

S A 1 6 | 1 | |||

A 1 6 |

| |||

S A 1 7 | 4 0 |

| ||

A 1 7 |

| |||

|

|

| ||

| 9 |

| NC | |

| W E # | NC | ||

| 2 4 | |||

| O E # | NC | ||

| 2 2 | |||

| CE# | NC | ||

| 1 0 | |||

| RP# |

| ||

|

|

|

C 1 3 1 | 2 8 F 0 0 2 B C |

0 . 1uF |

|

+ 1 2 V

2 |

![]() C 1 3 0 0 . 1uF

C 1 3 0 0 . 1uF

| XD[7:0] | 1 3 |

2 5 | XD0 |

|

2 6 | XD1 |

|

2 7 | XD2 |

|

2 8 | XD3 |

|

3 2 | XD4 |

|

3 3 | XD5 |

|

3 4 | XD6 |

|

3 5 | XD7 |

|

1 1 | V 5 _ 0 |

|

|

| |

3 1 |

|

|

3 0 | C 2 0 8 |

|

3 9 |

| |

2 3 | 0 . 1uF |

|

1

A

2 |

| THIS DRAWING CONTAINS INFORMATION WHICH HASNOT |

|

|

| |||

1 3 | P W R O K 5 2 1 | BEEN VERIFIED FOR MANUFACTURING AS AN END SERU Title |

|

| ||||

J22 |

| PRODUCT. | INTEL IS NOT RESPONSIBLE FORTHE | Size | BIOS/ Port 80 | Rev | ||

HDR3 |

| MISUSE OF THIS INFORMATIO. | Document Number | |||||

| C | {Doc} | D | |||||

|

|

|

|

|

| Date: | Thursday, February 25, 1999 | Sheet 2 0 of 2 2 |

B |

| C |

| D |

|

| E |

|