4

3

2

1

| A |

|

|

|

|

| B |

|

|

|

|

|

|

|

| C |

|

|

|

|

| D |

|

|

| E |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| T P 1 7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| V2.5 |

|

| TP |

|

|

|

|

|

|

|

|

| V 3 _ 3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| V 5 _ 0 |

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 1 |

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| U5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| V2 . 5 |

| 2 | Out | In | 3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 4 |

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| O u t T a b |

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| R15 |

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| C 1 6 2 |

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| C95 | 1 2 4 |

|

| C94 |

| |

|

|

|

| C93 | C 1 6 5 | C 1 7 3 | C 1 6 9 | C 1 0 1 | C 1 7 1 | C 1 7 0 |

|

|

|

|

|

| C 1 6 8 | C 1 6 4 | C 1 6 3 | 1% |

|

| 0 . 1uF |

| ||

|

|

|

|

|

|

|

|

|

| 1 0 0 u F |

|

|

|

| 1 0 u F | 4 | ||||||||||

|

|

|

| 4 7 u F | 0 . 01uF | 0 . 01uF | 0 . 01uF | 0 . 01uF | 0 . 01uF | 0 . 01uF |

|

|

|

|

|

| 0 . 01uF | 0 . 01uF | 0 . 01uF | 1 |

|

|

| |||

|

|

|

|

|

|

|

|

|

|

| Adj/GND |

|

|

| ||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| R16 | L T 1 17 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 1 2 4 |

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

| V 3 _ 3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

| 1% |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

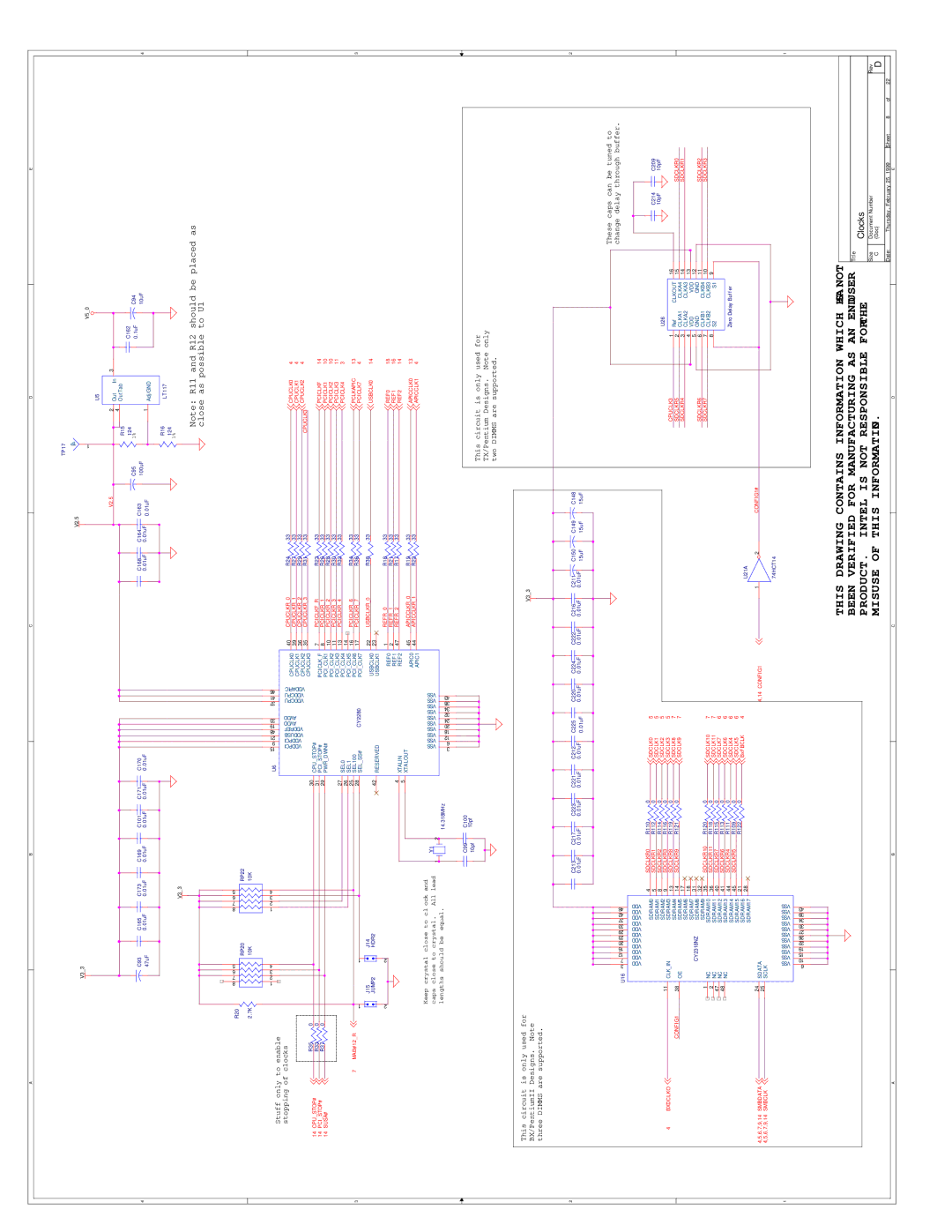

| Note: R11 and R12 should be placed as |

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| close as possible to U1 |

| ||||

|

|

| R20 | 8 7 6 5 |

| 8 7 6 5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| RP20 |

| RP22 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

| 2 .7K | 1 0 K |

| 1 0 K |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Stuff only to enable |

| 1 2 3 4 |

| 1 2 3 4 |

|

|

| U6 | 15 9 21 48 19 33 | 37 41 46 |

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| stopping of clocks |

|

|

|

|

|

|

|

| VDDPCI | VDDPCI VDDUSB VDDREF AVDD AVDD | VDDCPU VDDCPU VDDAPIC | CPUCLK2 | 3 6 | CPUCLKR _ 2 | R29 | 3 3 |

|

|

| CPUCLK2 | 4 |

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

| CPUCLK0 | 4 0 | CPUCLKR _ 0 | R24 | 3 3 |

|

|

| CPUCLK0 | 4 |

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

| 3 9 | CPUCLKR _ 1 | R27 | 3 3 |

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| CPUCLK1 |

|

|

| CPUCLK1 | 4 |

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

| R35 | 0 |

|

|

|

|

| 3 0 |

|

|

|

| CPUCLK3 | 3 5 | CPUCLKR _ 3 | R31 | 3 3 |

|

| CPUCLK3 |

|

|

|

|

|

1 4 | CPU _ STOP# |

|

|

|

|

| CPU _ STOP# |

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

R33 | 0 |

|

|

|

|

| 3 1 |

|

|

| 7 | PCICLKF_R | R23 | 3 3 |

|

|

| PCICLKF | 1 4 |

|

| |||||

1 4 | PCI _ STOP# | R37 | 0 |

|

|

|

|

| 2 9 | PCI _ STOP# |

|

| PCICLK_F | 8 | PCICLKR_1 | R26 | 3 3 |

|

|

|

|

| ||||

1 4 | SUSA# |

|

|

|

|

| PWR _ DWN# |

|

| PCI_CLK1 |

|

|

| PCICLK1 | 1 0 |

|

| |||||||||

|

|

|

|

|

|

|

|

|

| 1 0 | PCICLKR_2 | R28 | 3 3 |

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| PCI_CLK2 |

|

|

| PCICLK2 | 1 0 |

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| 1 1 | PCICLKR_3 | R30 | 3 3 |

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| PCI_CLK3 |

|

|

| PCICLK3 | 1 1 |

|

| |||||

|

|

|

|

|

|

|

|

| 2 7 |

|

|

|

| 1 3 | PCICLKR_4 | R32 | 3 3 |

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

| S E L 0 |

|

|

| PCI_CLK4 |

|

|

| PCICLK4 | 3 |

|

| ||||||

|

|

|

|

|

|

|

|

| 2 6 |

|

|

| 1 4 |

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

| S E L 1 |

|

|

| PCI_CLK5 | PCICLKR_6 | R34 | 3 3 |

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

| 2 5 |

|

|

| 1 6 |

|

|

| PCLKAPIC | 1 3 |

|

| ||||||

| 7 | M A B # 1 2 _ R |

|

|

|

|

|

| S E L 1 0 0 |

|

|

| PCI_CLK6 |

|

|

|

|

| ||||||||

|

|

|

|

|

|

| 2 8 |

| CY2280 |

| 1 7 | PCICLKR_7 | R36 | 3 3 |

|

|

|

| 3 | |||||||

| 1 | 1 |

|

|

|

|

|

|

|

|

| PCICLK7 | 4 |

| ||||||||||||

|

|

|

|

|

|

|

| SEL _ SS# |

| PCI_CLK7 |

|

|

|

|

|

|

|

|

| |||||||

J15 | J14 |

|

| USBCLK0 | 2 2 | USBCLKR _ 0 | R38 | 3 3 | USBCLK0 | 1 4 |

JUMP2 | HDR2 | 4 2 |

| 2 3 |

|

|

| |||

RESERVED | USBCLK1 |

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

| ||

2 | 2 |

|

| REF0 | 1 | REFR _ 0 | R18 | 3 3 | REF0 | 1 8 |

|

|

|

| 2 | REFR _ 1 | R21 | 3 3 | |||

|

|

|

| REF1 | REF1 | 1 6 | ||||

|

| 4 |

| 4 7 | REFR _ 2 | R17 | 3 3 | |||

|

| XTALIN | REF2 | REF2 | 1 4 | |||||

|

| 5 |

|

|

|

| ||||

|

| X T A L O U T |

| 4 5 | APICCLKR_0 | R19 | 3 3 |

|

| |

|

|

| APIC0 | APICCLK0 | 1 3 | |||||

|

|

|

| 4 4 | APICCLKR_1 | R22 | 3 3 | |||

|

|

|

| APIC1 | APICCLK1 | 4 | ||||

|

|

|

|

|

|

|

|

Keep | crystal close to cl ock and | Y1 |

| VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS | |

caps | close to crystal. | All lead | 2 | ||

lengths should be equal. |

| 1 | 14 . 318MHz | ||

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

| 3 6 12 18 20 24 32 34 38 43 |

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

| C99 | C 1 0 0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

| 10pf | 10pf |

|

|

|

|

|

|

|

|

|

|

| This circuit is only used for |

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| TX/Pentium Designs. | Note only |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| two DIMMS are supported. |

|

|

|

| |

This circuit is only used for |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| V 3 _ 3 |

|

|

|

|

|

|

|

|

| |

BX/PentiumII Designs. Note |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

three DIMMS are supported. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

| C 2 1 3 | C 2 1 7 | C 2 2 3 | C 2 2 1 | C 2 1 2 | C 2 2 5 | C 2 2 0 | C 2 2 4 | C 2 2 2 | C 2 1 6 | C 2 1 1 | C 1 5 0 | C 1 4 9 | C 1 4 8 |

|

|

|

| 2 | |

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||

|

|

|

|

|

|

|

| 0 . 01uF | 0 . 01uF | 0 . 01uF | 0 . 01uF | 0 . 01uF | 0 . 01uF | 0 . 01uF | 0 . 01uF | 0 . 01uF | 0 . 01uF | 0 . 01uF | 1 5 u F | 1 5 u F | 1 5 u F |

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| These caps can be tuned to | |

|

|

| U16 | 3 7 12 16 20 23 29 33 37 42 46 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| change delay through buffer. | |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

| VDD | VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

| SDRAM0 | 4 | SDCLKR0 |

| R 1 1 0 | 0 |

| SDCLK0 | 5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 5 | SDCLKR1 |

| R 1 1 2 | 0 |

|

|

|

|

|

|

|

|

|

|

|

| C 2 1 4 | C 2 0 9 | |||

|

|

|

|

|

| SDRAM1 |

|

| SDCLK1 | 5 |

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

| 8 | SDCLKR2 |

| R 1 1 4 | 0 |

|

|

|

|

|

|

|

|

|

|

|

| 1 0 p F | 1 0 p F | |||

|

|

|

|

|

| SDRAM2 |

|

| SDCLK2 | 5 |

|

|

|

|

|

|

|

|

| U26 |

| ||||||

|

| 1 1 |

|

|

| 9 | SDCLKR3 |

| R 1 1 6 | 0 |

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

4 | BXDCLKO | CLK_IN |

| SDRAM3 |

|

| SDCLK3 | 5 |

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

| 1 3 | SDCLKR8 |

| R 1 1 9 | 0 |

|

|

|

|

|

|

|

| CPUCLK3 | 1 |

|

| 1 6 |

| |||||||

|

|

|

|

|

| SDRAM4 |

|

| SDCLK8 | 7 |

|

|

|

|

|

|

| Ref | CLKOUT |

| |||||||

| CONFIG1 | 3 8 |

|

|

| 1 4 | SDCLKR9 |

| R 1 2 1 | 0 |

|

|

|

|

|

|

|

| SDCLKR5 | 2 | 1 5 | SDCLKR0 | |||||

| O E |

|

| SDRAM5 |

|

| SDCLK9 | 7 |

|

|

|

|

|

|

| CLKA1 | CLKA4 | ||||||||||

|

|

|

|

| 1 7 |

|

|

|

|

|

|

|

|

|

|

|

| SDCLKR4 | 3 | 1 4 | SDCLKR1 | ||||||

|

|

|

|

|

| SDRAM6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

| CLKA2 | CLKA3 | |||||

|

|

|

|

|

| 1 8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 4 | 1 3 |

| |||

|

|

|

|

|

| SDRAM7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| VDD | VDD |

| |||

|

|

|

|

| CY2318NZ | 3 1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 5 | 1 2 |

| |||

|

|

|

|

| SDRAM8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

| SDCLKR6 | GND | GND | SDCLKR2 | ||||

|

|

|

|

| 3 2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

| 6 | 1 1 | ||||||

|

| 1 |

|

|

| SDRAM9 | 3 5 | SDCLKR10 |

| R 1 2 0 | 0 |

| SDCLK10 | 7 |

|

|

|

|

|

|

| SDCLKR7 | 7 | CLKB1 | CLKB4 | 1 0 | SDCLKR3 |

|

| NC |

|

| SDRAM10 |

|

|

|

|

|

|

|

|

| CLKB2 | CLKB3 | |||||||||||

|

| 2 |

|

| 3 6 | SDCLKR11 |

| R 1 1 8 | 0 |

|

|

|

|

|

|

|

|

| 8 | 9 |

| ||||||

|

| NC |

|

| SDRAM11 |

|

| SDCLK11 | 7 |

|

|

|

|

|

|

|

| S 2 | S 1 |

| |||||||

|

| 4 7 |

|

| 4 0 | SDCLKR7 |

| R 1 1 5 | 0 |

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

| NC |

|

| SDRAM12 |

|

| SDCLK7 | 6 |

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

| 4 8 |

|

| 4 1 | SDCLKR6 |

| R 1 1 3 | 0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

| NC |

|

| SDRAM13 |

|

| SDCLK6 | 6 |

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

| 4 4 | SDCLKR4 |

| R 1 1 1 | 0 |

|

|

|

|

|

|

|

|

|

| Zero Delay Buffer |

|

| |||||

|

|

|

|

|

| SDRAM14 |

|

| SDCLK4 | 6 |

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

| 4 5 | SDCLKR5 |

| R 1 0 9 | 0 |

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

| SDRAM15 |

|

| SDCLK5 | 6 |

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

| 2 1 |

|

| R 1 2 2 | 0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

| SDRAM16 |

|

|

| BxFBCLK | 4 |

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

| 2 8 |

|

|

|

|

|

|

|

|

| U21A |

|

|

|

|

|

|

|

| |||

|

|

|

|

|

| SDRAM17 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

4,5,6,7,9,14 | S M B D A T A | 2 4 | S D A T A |

|

|

|

|

|

|

|

|

|

| 4,14 CONFIG1 |

|

| 1 | 2 |

| CONFIG1# |

|

|

|

|

| ||

2 5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

4,5,6,7,9,14 | SMBCLK | SCLK |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

| VSS | VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS |

|

|

|

|

|

|

|

|

|

|

|

| 74HCT14 |

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 1 | |||

|

|

|

| 6 10 15 19 22 26 27 30 34 39 43 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

| THIS DRAWING CONTAINS INFORMATION WHICH HAS NOT |

|

|

| |||

|

| BEEN VERIFIED FOR MANUFACTURING AS AN ENDUSER Title |

|

| ||||

|

| PRODUCT. | INTEL IS NOT RESPONSIBLE FORTHE |

| Clocks |

| ||

|

| MISUSE OF THIS INFORMATIO. | Size | Document Number | Rev | |||

|

| C | {Doc} | D | ||||

|

|

|

|

|

| Date: | Thursday, February 25, 1999 | Sheet 8 of 2 2 |

A | B | C |

| D |

|

| E |

|