3.3.3Memory Subsystem

The memory subsystem is designed to support Double Data Rate 2 (DDR2) Synchronous Dynamic Random Access Memory (SDRAM) using the Intel® E7520 MCH. The MCH provides two independent DDR channels, which support

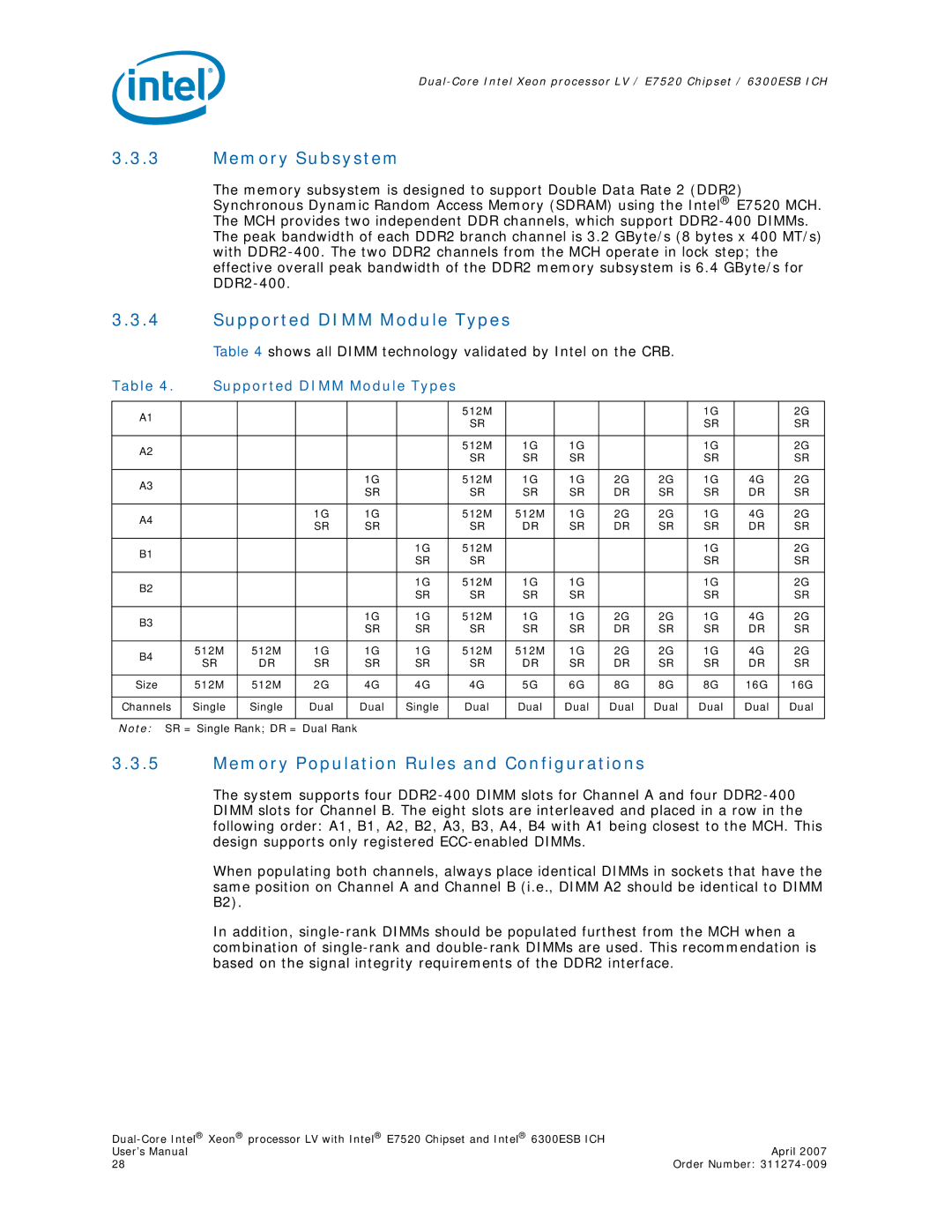

3.3.4Supported DIMM Module Types

Table 4 shows all DIMM technology validated by Intel on the CRB.

Table 4. | Supported DIMM Module Types |

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A1 |

|

|

|

|

|

| 512M |

|

|

|

| 1G |

| 2G |

|

|

|

|

|

| SR |

|

|

|

| SR |

| SR | |

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A2 |

|

|

|

|

|

| 512M | 1G | 1G |

|

| 1G |

| 2G |

|

|

|

|

|

| SR | SR | SR |

|

| SR |

| SR | |

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A3 |

|

|

| 1G |

|

| 512M | 1G | 1G | 2G | 2G | 1G | 4G | 2G |

|

|

| SR |

|

| SR | SR | SR | DR | SR | SR | DR | SR | |

|

|

|

|

|

| |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A4 |

|

| 1G | 1G |

|

| 512M | 512M | 1G | 2G | 2G | 1G | 4G | 2G |

|

| SR | SR |

|

| SR | DR | SR | DR | SR | SR | DR | SR | |

|

|

|

|

| ||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

B1 |

|

|

|

| 1G |

| 512M |

|

|

|

| 1G |

| 2G |

|

|

|

| SR |

| SR |

|

|

|

| SR |

| SR | |

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

B2 |

|

|

|

| 1G |

| 512M | 1G | 1G |

|

| 1G |

| 2G |

|

|

|

| SR |

| SR | SR | SR |

|

| SR |

| SR | |

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

B3 |

|

|

| 1G | 1G |

| 512M | 1G | 1G | 2G | 2G | 1G | 4G | 2G |

|

|

| SR | SR |

| SR | SR | SR | DR | SR | SR | DR | SR | |

|

|

|

|

| ||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

B4 | 512M | 512M | 1G | 1G | 1G |

| 512M | 512M | 1G | 2G | 2G | 1G | 4G | 2G |

SR | DR | SR | SR | SR |

| SR | DR | SR | DR | SR | SR | DR | SR | |

|

| |||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Size | 512M | 512M | 2G | 4G | 4G |

| 4G | 5G | 6G | 8G | 8G | 8G | 16G | 16G |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Channels | Single | Single | Dual | Dual | Single |

| Dual | Dual | Dual | Dual | Dual | Dual | Dual | Dual |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Note: SR = Single Rank; DR = Dual Rank

3.3.5Memory Population Rules and Configurations

The system supports four

When populating both channels, always place identical DIMMs in sockets that have the same position on Channel A and Channel B (i.e., DIMM A2 should be identical to DIMM B2).

In addition,

| |

User’s Manual | April 2007 |

28 | Order Number: |