Intel® IQ80219 General Purpose PCI Processor Evaluation Platform

Hardware Reference Section

3.4Memory Subsystem

Memory subsystem consists of the SDRAM as well as the Flash memory subsystems.

3.4.1DDR SDRAM

The DDR SDRAM interface consists of a

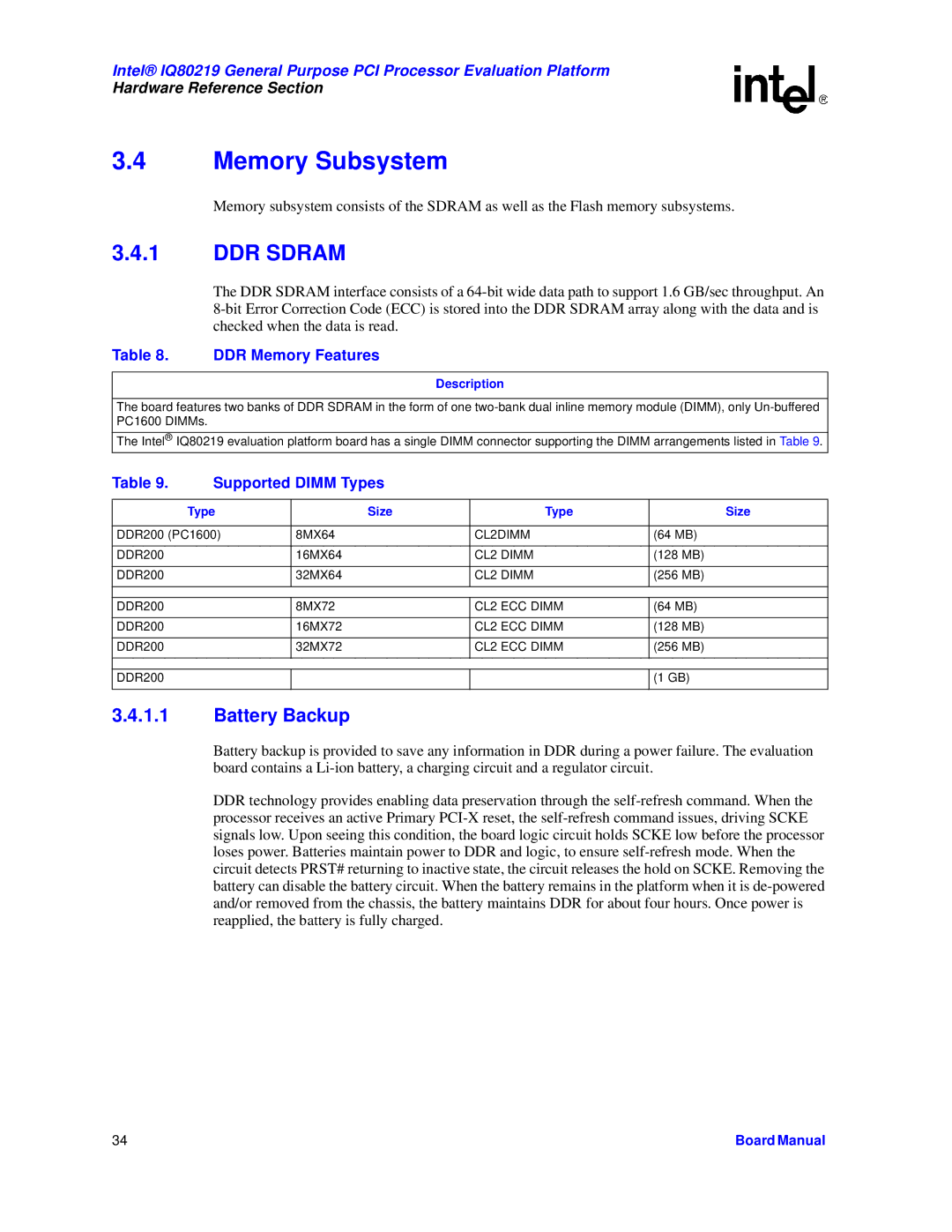

Table 8. DDR Memory Features

Description

The board features two banks of DDR SDRAM in the form of one

The Intel® IQ80219 evaluation platform board has a single DIMM connector supporting the DIMM arrangements listed in Table 9.

Table 9. | Supported DIMM Types |

|

| |

|

|

|

|

|

| Type | Size | Type | Size |

|

|

|

| |

DDR200 (PC1600) | 8MX64 | CL2DIMM | (64 MB) | |

|

|

|

|

|

DDR200 |

| 16MX64 | CL2 DIMM | (128 MB) |

|

|

|

|

|

DDR200 |

| 32MX64 | CL2 DIMM | (256 MB) |

|

|

|

|

|

|

|

|

|

|

DDR200 |

| 8MX72 | CL2 ECC DIMM | (64 MB) |

|

|

|

|

|

DDR200 |

| 16MX72 | CL2 ECC DIMM | (128 MB) |

|

|

|

|

|

DDR200 |

| 32MX72 | CL2 ECC DIMM | (256 MB) |

|

|

|

|

|

|

|

|

|

|

DDR200 |

|

|

| (1 GB) |

|

|

|

|

|

3.4.1.1Battery Backup

Battery backup is provided to save any information in DDR during a power failure. The evaluation board contains a

DDR technology provides enabling data preservation through the

34 | Board Manual |