Intel® IQ80219 General Purpose PCI Processor Evaluation Platform

Hardware Reference Section

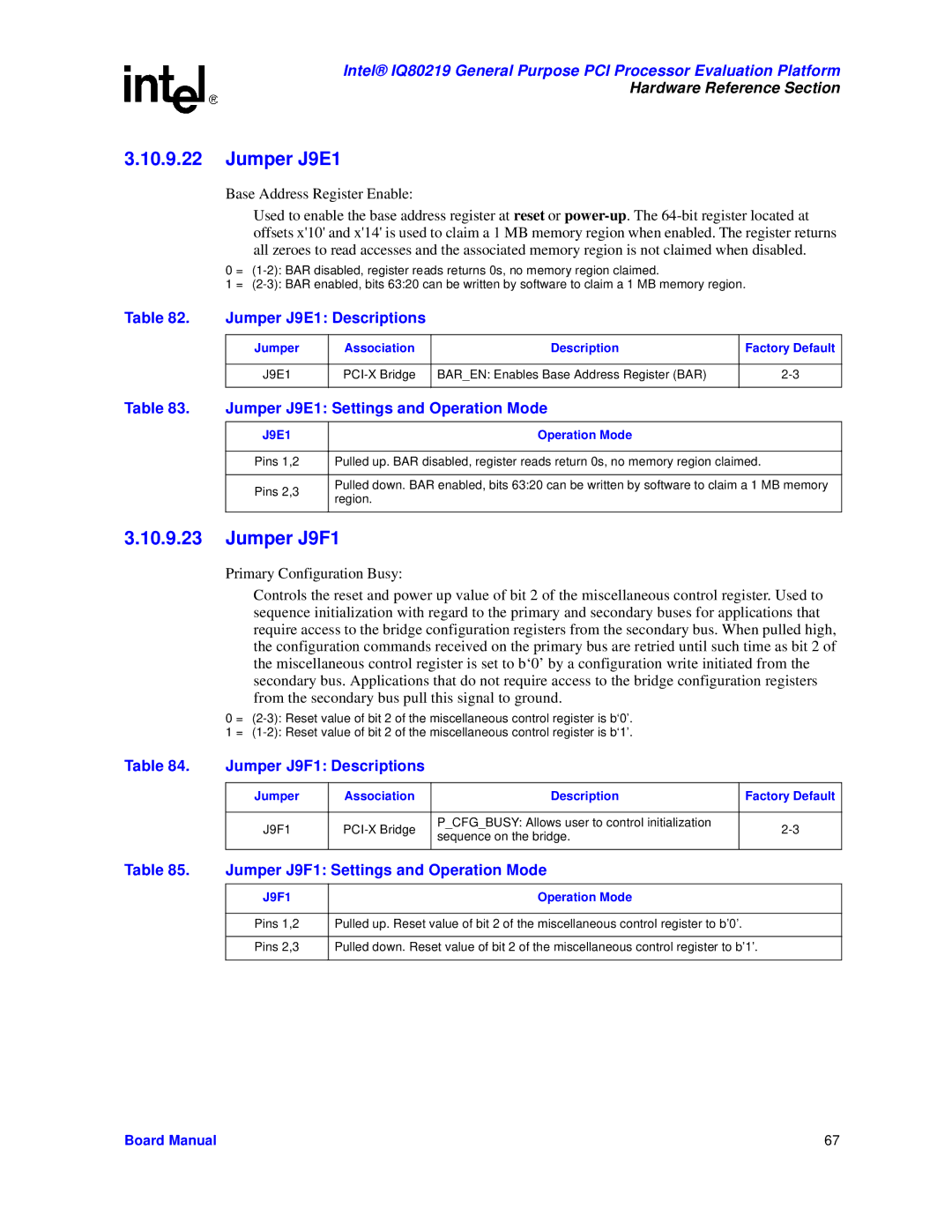

3.10.9.22Jumper J9E1

Base Address Register Enable:

Used to enable the base address register at reset or

0 =

1 =

Table 82. | Jumper J9E1: Descriptions |

|

| |

|

|

|

|

|

| Jumper | Association | Description | Factory Default |

|

|

|

|

|

| J9E1 | BAR_EN: Enables Base Address Register (BAR) | ||

|

|

|

|

|

Table 83. | Jumper J9E1: Settings and Operation Mode |

| ||

|

|

|

|

|

| J9E1 |

| Operation Mode |

|

|

|

| ||

| Pins 1,2 | Pulled up. BAR disabled, register reads return 0s, no memory region claimed. | ||

|

|

| ||

| Pins 2,3 | Pulled down. BAR enabled, bits 63:20 can be written by software to claim a 1 MB memory | ||

| region. |

|

| |

|

|

|

| |

|

|

|

|

|

3.10.9.23Jumper J9F1

Primary Configuration Busy:

Controls the reset and power up value of bit 2 of the miscellaneous control register. Used to sequence initialization with regard to the primary and secondary buses for applications that require access to the bridge configuration registers from the secondary bus. When pulled high, the configuration commands received on the primary bus are retried until such time as bit 2 of the miscellaneous control register is set to b‘0’ by a configuration write initiated from the secondary bus. Applications that do not require access to the bridge configuration registers from the secondary bus pull this signal to ground.

0 =

1 =

Table 84. | Jumper J9F1: Descriptions |

|

| |

|

|

|

|

|

| Jumper | Association | Description | Factory Default |

|

|

|

|

|

| J9F1 | P_CFG_BUSY: Allows user to control initialization | ||

| sequence on the bridge. | |||

|

|

|

| |

|

|

|

|

|

Table 85. | Jumper J9F1: Settings and Operation Mode | |

| J9F1 | Operation Mode |

|

|

|

| Pins 1,2 | Pulled up. Reset value of bit 2 of the miscellaneous control register to b’0’. |

|

|

|

| Pins 2,3 | Pulled down. Reset value of bit 2 of the miscellaneous control register to b’1’. |

|

|

|

Board Manual | 67 |