IQ80310 and IQ80219 Comparisons | A |

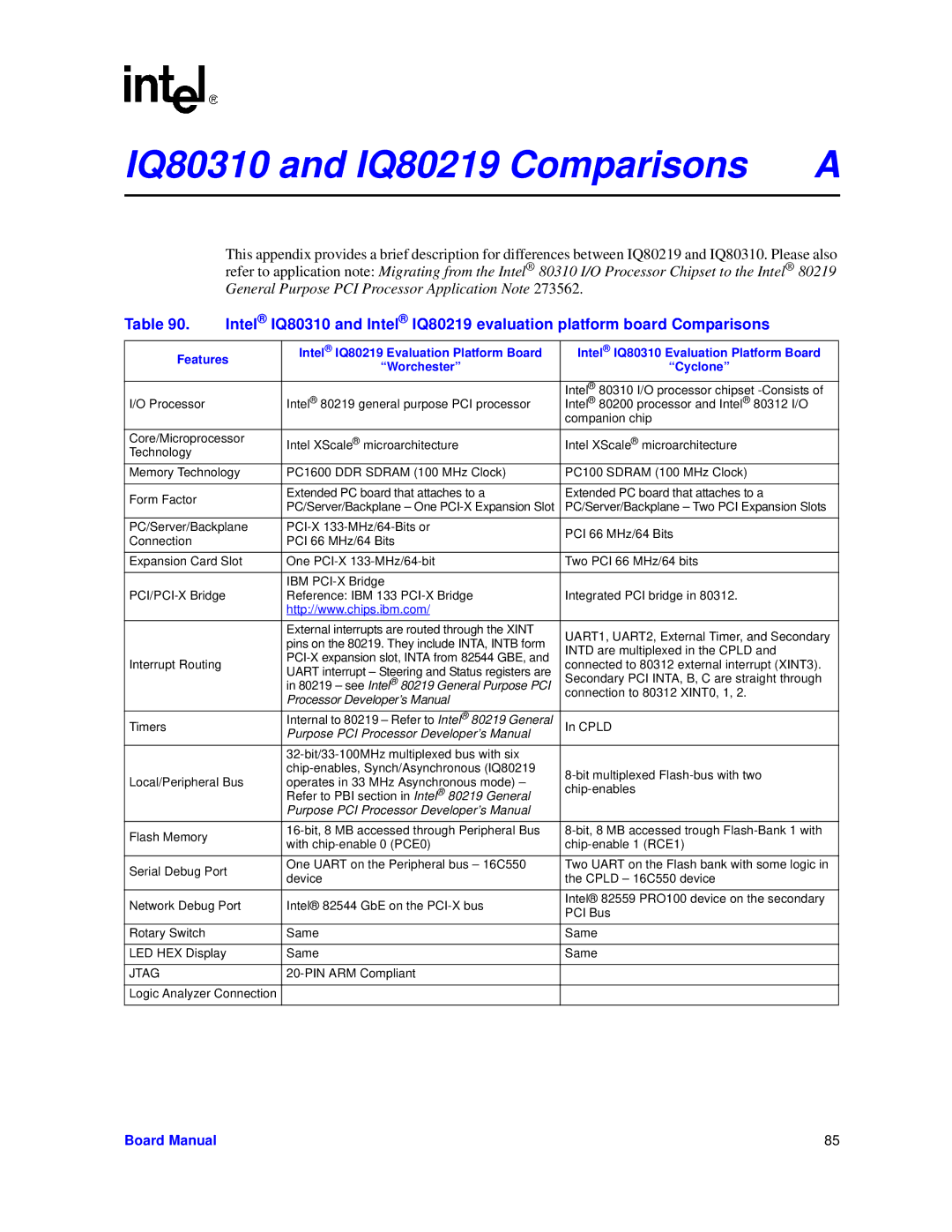

This appendix provides a brief description for differences between IQ80219 and IQ80310. Please also refer to application note: Migrating from the Intel® 80310 I/O Processor Chipset to the Intel® 80219 General Purpose PCI Processor Application Note 273562.

Table 90. | Intel® | IQ80310 and Intel® IQ80219 evaluation platform board Comparisons | ||

Features |

| Intel® IQ80219 Evaluation Platform Board | Intel® IQ80310 Evaluation Platform Board | |

| “Worchester” | “Cyclone” | ||

|

|

| ||

|

|

|

|

|

|

|

|

| Intel® 80310 I/O processor chipset |

I/O Processor |

|

| Intel®80219 general purpose PCI processor | Intel® 80200 processor and Intel®80312 I/O |

|

|

|

| companion chip |

|

|

|

| |

Core/Microprocessor |

| Intel XScale® microarchitecture | Intel XScale® microarchitecture | |

Technology |

|

|

|

|

Memory Technology |

| PC1600 DDR SDRAM (100 MHz Clock) | PC100 SDRAM (100 MHz Clock) | |

|

|

|

|

|

Form Factor |

|

| Extended PC board that attaches to a | Extended PC board that attaches to a |

|

| PC/Server/Backplane – One | PC/Server/Backplane – Two PCI Expansion Slots | |

|

|

| ||

|

|

|

| |

PC/Server/Backplane |

| PCI 66 MHz/64 Bits | ||

Connection |

|

| PCI 66 MHz/64 Bits | |

|

|

| ||

|

|

|

| |

Expansion Card Slot |

| One | Two PCI 66 MHz/64 bits | |

|

|

|

|

|

|

|

| IBM |

|

|

| Reference: IBM 133 | Integrated PCI bridge in 80312. | |

|

|

| http://www.chips.ibm.com/ |

|

|

|

|

|

|

|

|

| External interrupts are routed through the XINT | UART1, UART2, External Timer, and Secondary |

|

|

| pins on the 80219. They include INTA, INTB form | |

|

|

| INTD are multiplexed in the CPLD and | |

|

|

| ||

Interrupt Routing |

|

| connected to 80312 external interrupt (XINT3). | |

|

| UART interrupt – Steering and Status registers are | ||

|

|

| Secondary PCI INTA, B, C are straight through | |

|

|

| in 80219 – see Intel® 80219 General Purpose PCI | |

|

|

| connection to 80312 XINT0, 1, 2. | |

|

|

| Processor Developer’s Manual | |

|

|

|

| |

|

|

|

|

|

Timers |

|

| Internal to 80219 – Refer to Intel® 80219 General | In CPLD |

|

| Purpose PCI Processor Developer’s Manual | ||

|

|

|

| |

|

|

|

|

|

|

|

|

| |

|

|

| ||

Local/Peripheral Bus |

| operates in 33 MHz Asynchronous mode) – | ||

| ||||

|

|

| Refer to PBI section in Intel® 80219 General | |

|

|

|

| |

|

|

| Purpose PCI Processor Developer’s Manual |

|

|

|

|

|

|

Flash Memory |

|

| ||

|

| with | ||

|

|

| ||

|

|

|

|

|

Serial Debug Port |

| One UART on the Peripheral bus – 16C550 | Two UART on the Flash bank with some logic in | |

| device | the CPLD – 16C550 device | ||

|

|

| ||

|

|

|

|

|

Network Debug Port |

| Intel® 82544 GbE on the | Intel® 82559 PRO100 device on the secondary | |

| PCI Bus | |||

|

|

|

| |

|

|

|

|

|

Rotary Switch |

|

| Same | Same |

|

|

|

| |

LED HEX Display |

| Same | Same | |

|

|

|

|

|

JTAG |

|

|

| |

|

|

| ||

Logic Analyzer Connection |

|

| ||

|

|

|

|

|

Board Manual | 85 |