VXI Technology, Inc.

|

|

| *ESR? |

|

|

|

|

|

|

|

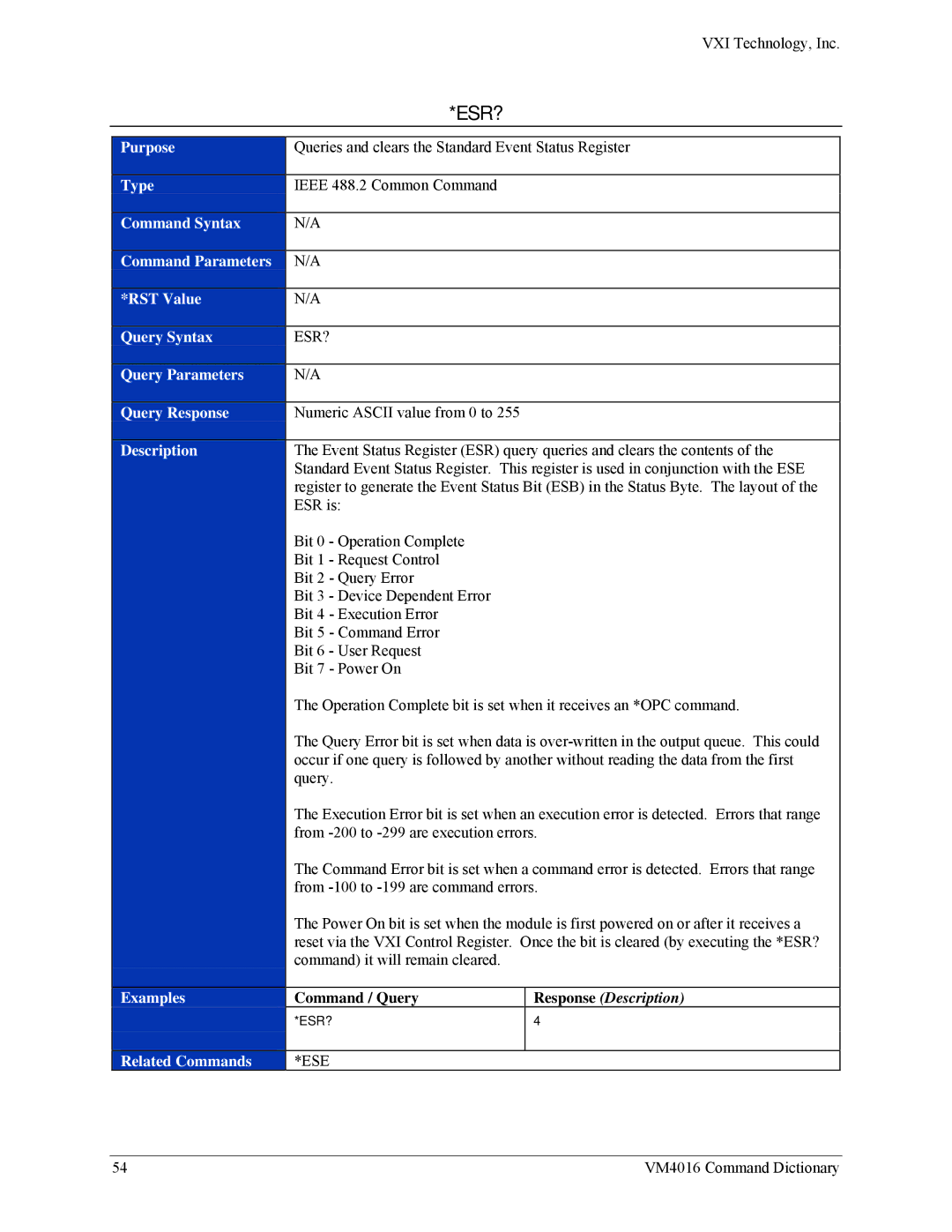

| Purpose | Queries and clears the Standard Event Status Register | |

|

|

|

|

|

|

| Type | IEEE 488.2 Common Command |

|

|

|

|

|

|

|

| Command Syntax | N/A |

|

|

|

|

|

|

|

| Command Parameters | N/A |

|

|

|

|

|

|

|

| *RST Value | N/A |

|

|

|

|

|

|

|

| Query Syntax | ESR? |

|

|

|

|

|

|

|

| Query Parameters | N/A |

|

|

|

|

|

|

|

| Query Response | Numeric ASCII value from 0 to 255 |

|

|

|

|

|

|

|

| Description | The Event Status Register (ESR) query queries and clears the contents of the | |

|

|

| Standard Event Status Register. This register is used in conjunction with the ESE | |

|

|

| register to generate the Event Status Bit (ESB) in the Status Byte. The layout of the | |

|

|

| ESR is: |

|

|

|

| Bit 0 - Operation Complete |

|

|

|

| Bit 1 - Request Control |

|

|

|

| Bit 2 - Query Error |

|

|

|

| Bit 3 - Device Dependent Error |

|

|

|

| Bit 4 - Execution Error |

|

|

|

| Bit 5 - Command Error |

|

|

|

| Bit 6 - User Request |

|

|

|

| Bit 7 - Power On |

|

|

|

| The Operation Complete bit is set when it receives an *OPC command. | |

|

|

| The Query Error bit is set when data is | |

|

|

| occur if one query is followed by another without reading the data from the first | |

|

|

| query. |

|

|

|

| The Execution Error bit is set when an execution error is detected. Errors that range | |

|

|

| from | |

|

|

| The Command Error bit is set when a command error is detected. Errors that range | |

|

|

| from | |

|

|

| The Power On bit is set when the module is first powered on or after it receives a | |

|

|

| reset via the VXI Control Register. Once the bit is cleared (by executing the *ESR? | |

|

|

| command) it will remain cleared. |

|

|

|

|

|

|

|

| Examples | Command / Query | Response (Description) |

|

|

| *ESR? | 4 |

|

|

|

|

|

|

| Related Commands | *ESE |

|

54 | VM4016 Command Dictionary |