CY7C1441AV33

CY7C1443AV33,CY7C1447AV33

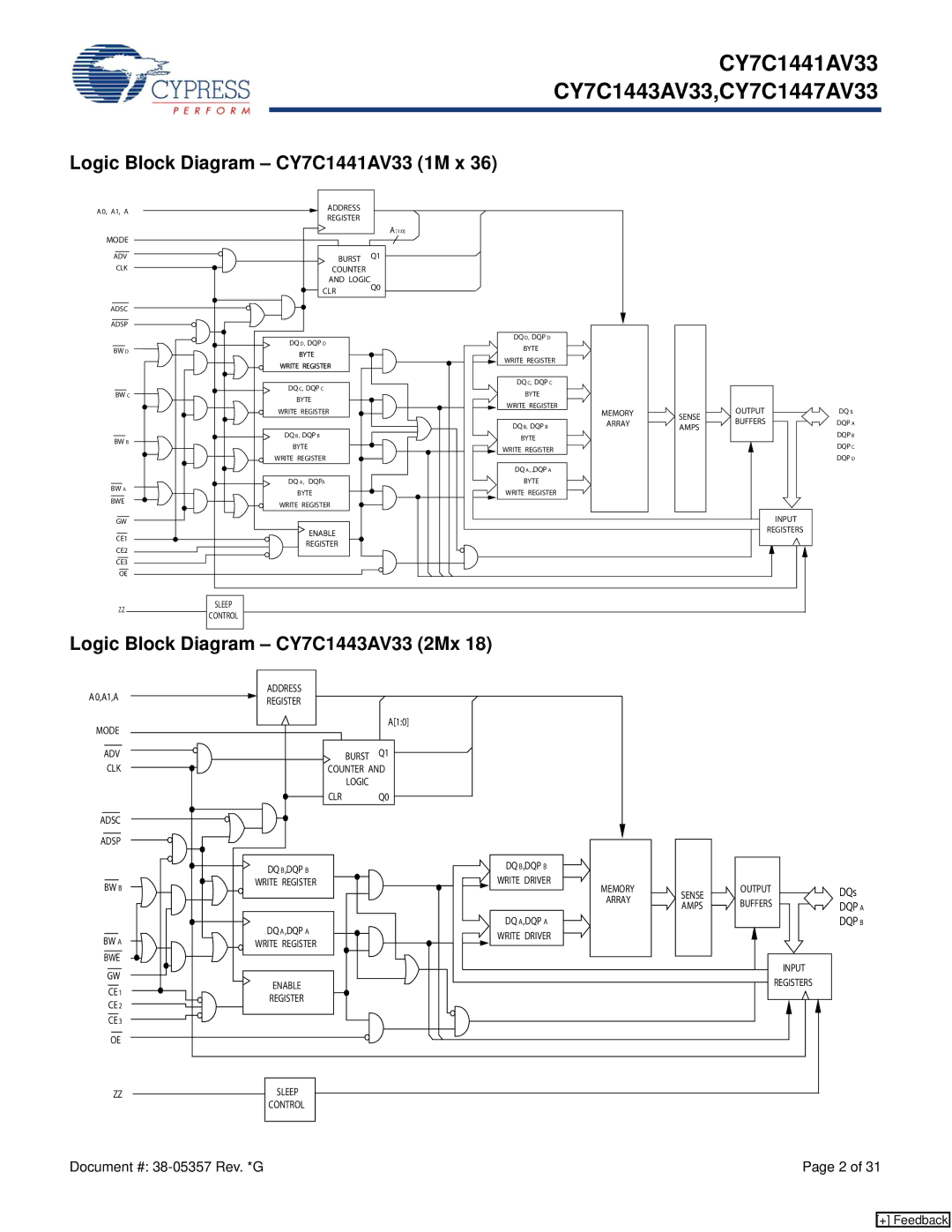

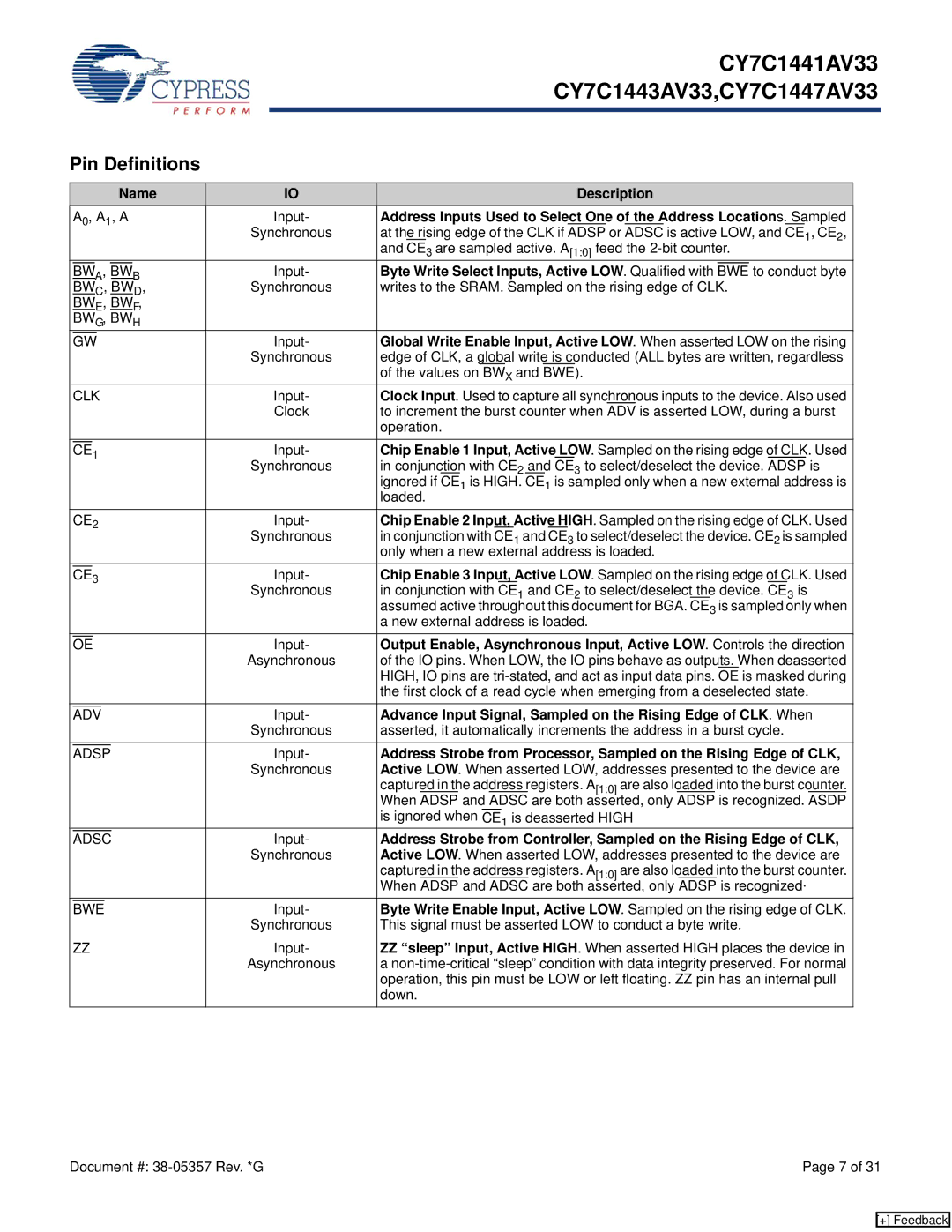

Logic Block Diagram – CY7C1447AV33 (512K x 72)

A0, A1,A | ADDRESS |

|

REGISTER |

| |

|

| |

| A[1:0] | |

MODE |

|

|

ADV | BURST | Q1 |

CLK | COUNTER |

|

| AND LOGIC | |

| CLR | Q0 |

ADSC |

|

|

ADSP |

|

|

BW H | DQ H, DQPH |

|

WRITE REGISTER |

| |

BW G | DQ F, DQPF |

|

WRITE REGISTER |

| |

BW F | DQ F, DQPF |

|

WRITE REGISTER |

| |

BW E | DQ E, DQPE |

|

WRITE REGISTER |

| |

BW D | DQ D, DQPD |

|

WRITE REGISTER |

| |

BW C | DQ C, DQPC |

|

WRITE REGISTER |

| |

BW B | DQ B, DQPB |

|

WRITE REGISTER |

| |

BW A | DQ A, DQPA |

|

WRITE REGISTER |

| |

BWE |

| |

|

| |

GW | ENABLE |

|

CE1 |

| |

REGISTER |

| |

CE2 |

| |

|

| |

CE3 |

|

|

OE |

|

|

ZZ | SLEEP |

|

CONTROL |

| |

|

| |

DQ H, DQPH WRITE DRIVER

DQ G, DQPG WRITE DRIVER

DQ F, DQPF WRITE DRIVER

DQBYTE, DQP“a”E

WRITE DRIVER

DQ D, DQPD WRITE DRIVER

DQ C, DQPC WRITE DRIVER

DQ B, DQPB WRITE DRIVER

DQ A, DQPA WRITE DRIVER

MEMORY

ARRAY

SENSE AMPS

OUTPUT BUFFERS

DQs

DQP A

DQP B

DQP C

DQP D

DQP E

DQP F

DQP G

DQP H

INPUT

REGISTERS

Document #: | Page 3 of 31 |

[+] Feedback