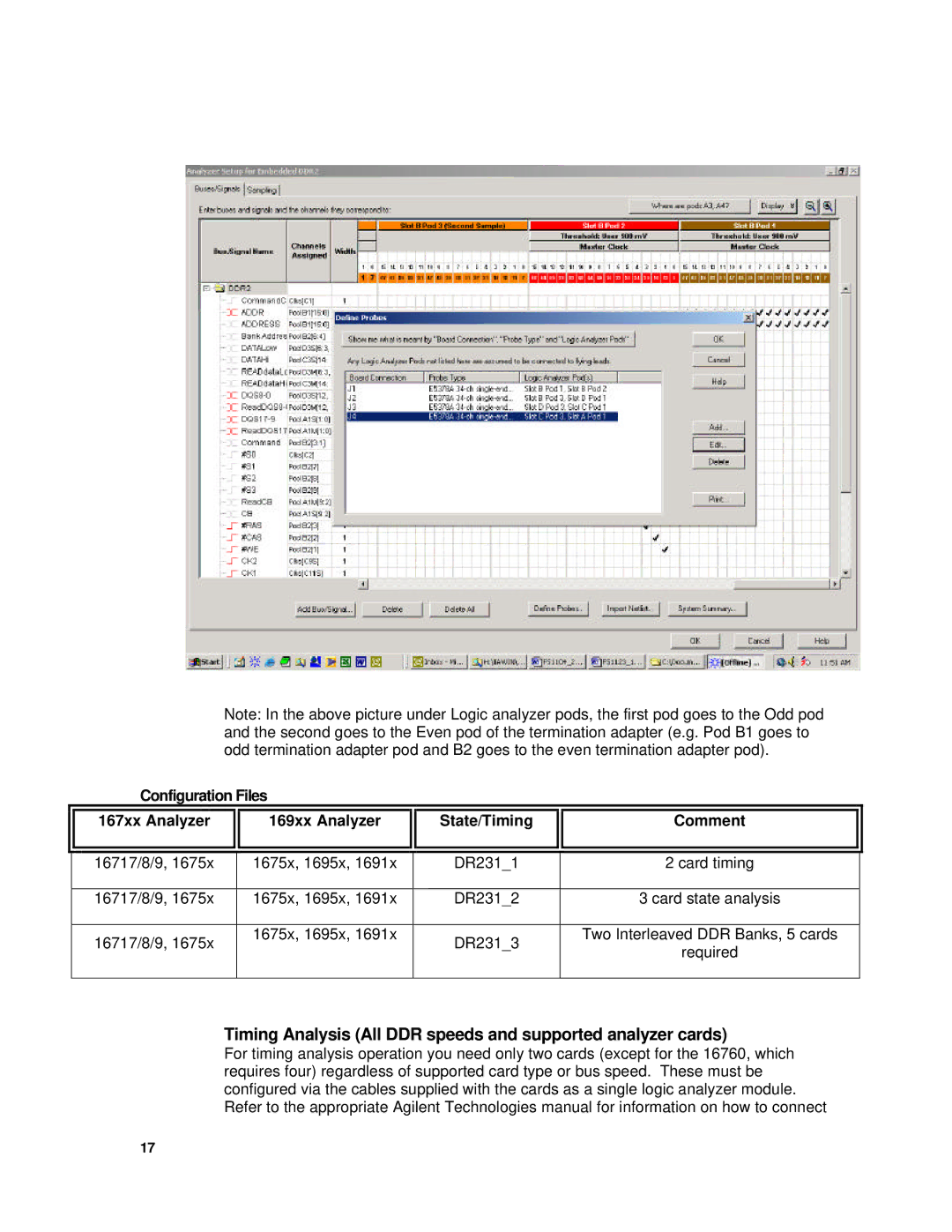

Note: In the above picture under Logic analyzer pods, the first pod goes to the Odd pod and the second goes to the Even pod of the termination adapter (e.g. Pod B1 goes to odd termination adapter pod and B2 goes to the even termination adapter pod).

Configuration Files

167xx Analyzer

169xx Analyzer

State/Timing

Comment

| 16717/8/9, 1675x | 1675x, 1695x, 1691x | DR231_1 | 2 card timing |

|

|

|

|

|

|

|

| 16717/8/9, 1675x | 1675x, 1695x, 1691x | DR231_2 | 3 card state analysis |

|

|

|

|

|

|

|

| 16717/8/9, 1675x | 1675x, 1695x, 1691x | DR231_3 | Two Interleaved DDR Banks, 5 cards |

|

|

| required |

| ||

|

|

|

|

| |

|

|

|

|

|

|

Timing Analysis (All DDR speeds and supported analyzer cards)

For timing analysis operation you need only two cards (except for the 16760, which requires four) regardless of supported card type or bus speed. These must be configured via the cables supplied with the cards as a single logic analyzer module. Refer to the appropriate Agilent Technologies manual for information on how to connect

17