Chapter 3 | Hardware |

Ethernet Interfaces (J10, J11)

The Ethernet solution is provided by two Intel 82551ER PCI controller chips, which consists of both the Media Access Controller (MAC) and the physical layer (PHY) combined into a single component solution. The 82551ER is a

•Backward software compatible to the 82559, 82558, and 82557

•Chained memory structure

•Full duplex or

•Full duplex support at 10Mbps and 100Mbps

•In

•IEEE 802.3 10BaseT/100BaseT compatible physical layer to wire transformer

•2 LED support for each port (speed, and link and activity are shared)

•Data transmission with minimum interframe spacing (IFS).

•IEEE 802.3u

•3kB transmit and 3kB receive FIFOs (helps prevent data underflow and overflow)

•IEEE 802.3x

•Improved dynamic transmit chaining with multiple priorities transmit queues

•Each Ethernet port has a

•Each Ethernet port controller connected to Primary PCI bus

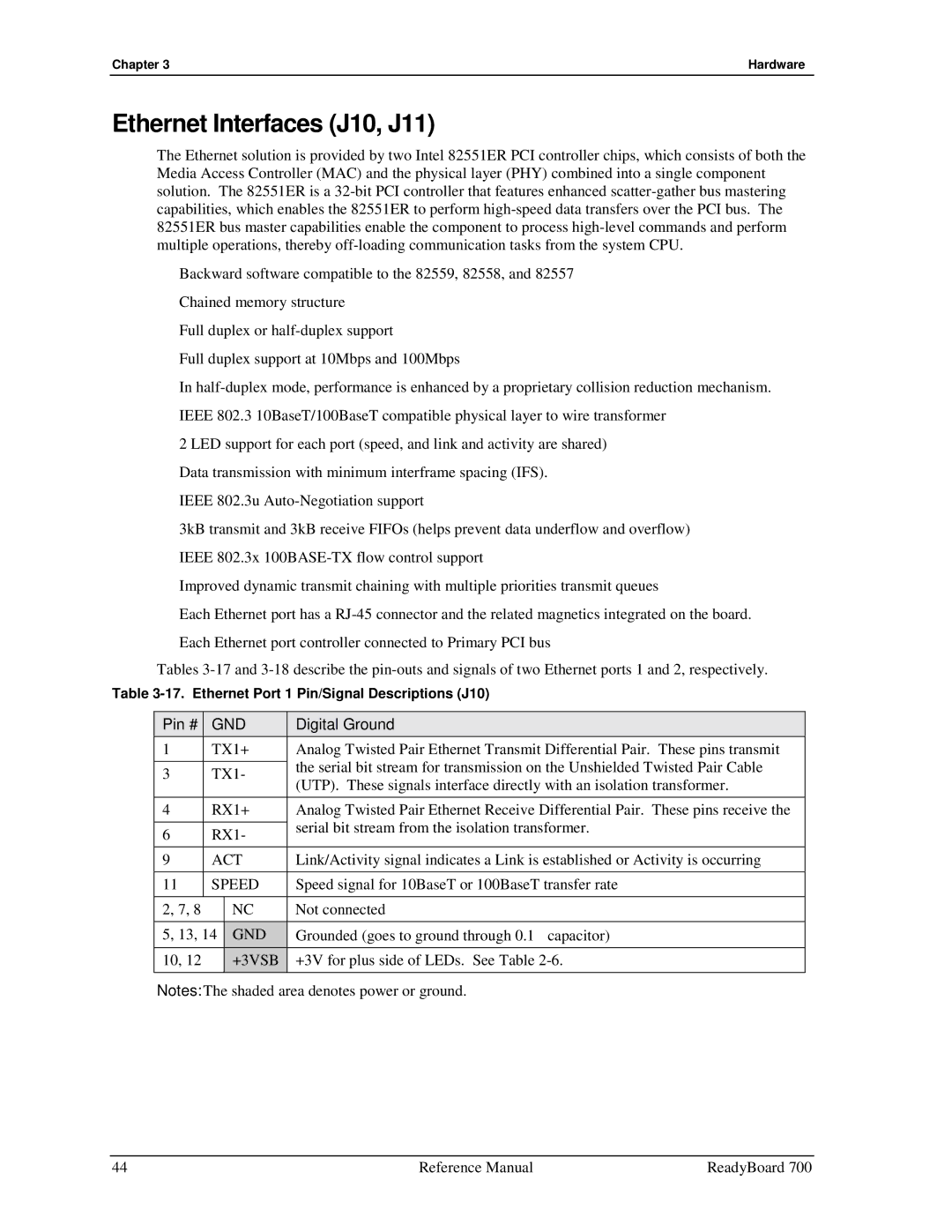

Tables

Table

Pin # | GND | Digital Ground | ||

1 | TX1+ | Analog Twisted Pair Ethernet Transmit Differential Pair. These pins transmit | ||

|

|

| the serial bit stream for transmission on the Unshielded Twisted Pair Cable | |

3 | TX1- | |||

(UTP). These signals interface directly with an isolation transformer. | ||||

|

|

| ||

|

|

|

| |

4 | RX1+ | Analog Twisted Pair Ethernet Receive Differential Pair. These pins receive the | ||

|

|

| serial bit stream from the isolation transformer. | |

6 | RX1- | |||

| ||||

|

|

|

| |

9 | ACT | Link/Activity signal indicates a Link is established or Activity is occurring | ||

|

|

|

| |

11 | SPEED | Speed signal for 10BaseT or 100BaseT transfer rate | ||

|

|

|

| |

2, 7, 8 |

| NC | Not connected | |

|

|

| ||

5, 13, 14 | GND | Grounded (goes to ground through 0.1∝ capacitor) | ||

10, 12 |

| +3VSB | +3V for plus side of LEDs. See Table | |

|

|

|

| |

Notes: The shaded area denotes power or ground.

44 | Reference Manual | ReadyBoard 700 |