Chapter 3 | Hardware |

Pin # |

| Signal | Description |

39 |

| FPDEN | Flat Panel Data Enable – This signal to settle the horizontal display position. |

|

|

|

|

40 |

| FP0 | Flat Panel Data Output 0 – Refer to |

|

|

|

|

41 |

| FPCLKS | Flat Panel Shift clock – This signal can be inverted by jumper JP1. |

|

|

|

|

42 |

| VEEON | Voltage On – This signal is high (+5V) when ENVEE & Power Good are High |

|

|

|

|

43 |

| ENVDD | Flat Panel Enable VDD – This is power sequencing output for LCD driver |

|

|

|

|

44 |

| FPVS | Flat Panel VSync (FLM) – This signal is digital monitor equivalent of VSYNC |

|

|

|

|

45 |

| ENVEE | Flat Panel Enable VEE – This signal is used for power sequencing |

|

|

|

|

46 |

| FPHS | Flat Panel HSync (LP) – This signal is the digital monitor equivalent of HSYNC |

|

|

|

|

47, 48 |

| GND | Ground |

49, 50 |

| +12V | +12V (this voltage is supplied externally from the AT/ATX power supply input |

|

|

| connector. It may also be used by the PCI bus or ISA bus. |

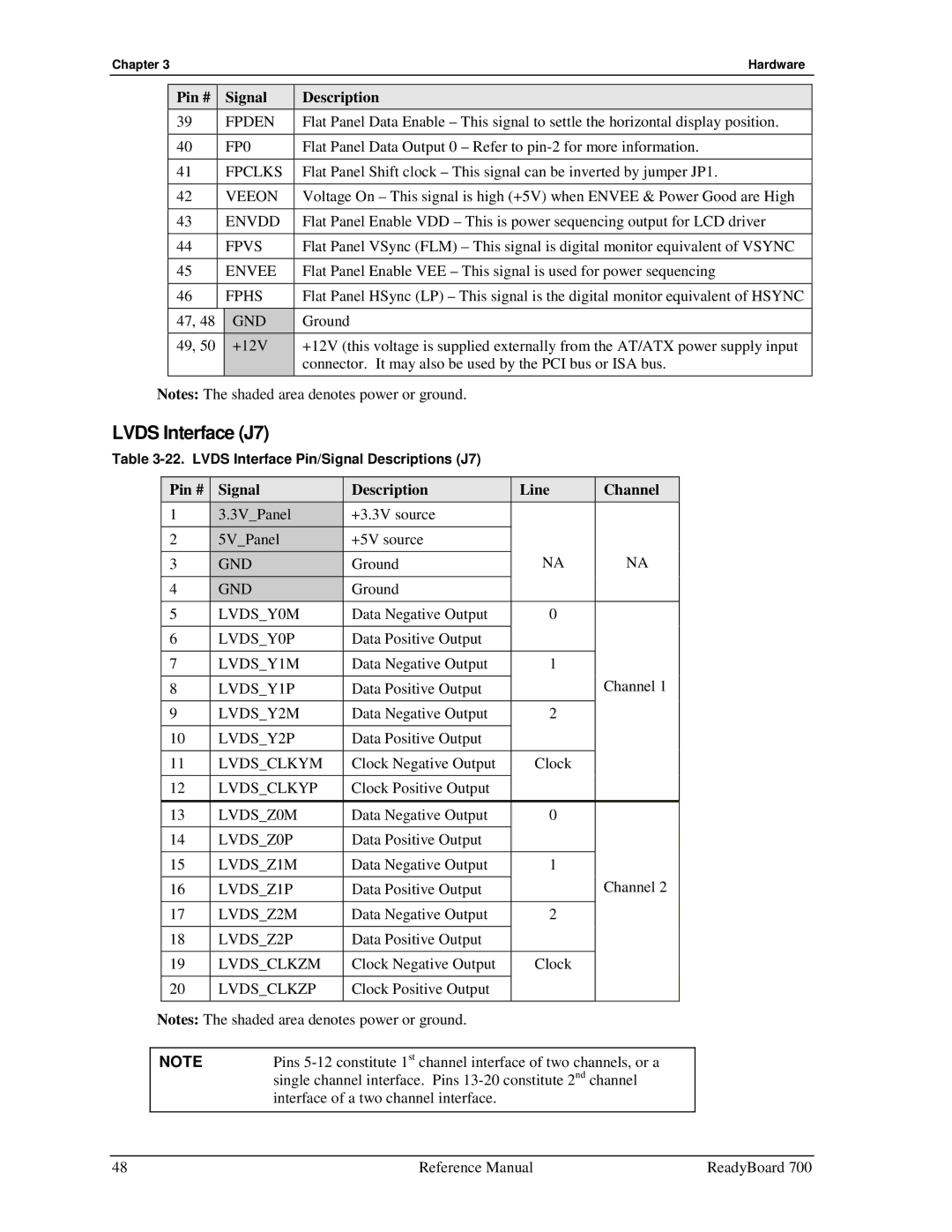

Notes: The shaded area denotes power or ground.

LVDS Interface (J7)

Table

Pin # Signal

Description

Line

Channel

1 | 3.3V_Panel | +3.3V source |

|

|

2 | 5V_Panel | +5V source |

|

|

3 | GND | Ground | NA | NA |

4 | GND | Ground |

|

|

5 | LVDS_Y0M | Data Negative Output | 0 |

|

6 | LVDS_Y0P | Data Positive Output |

|

|

|

|

|

|

|

7 | LVDS_Y1M | Data Negative Output | 1 |

|

|

|

|

| Channel 1 |

8 | LVDS_Y1P | Data Positive Output |

| |

9 | LVDS_Y2M | Data Negative Output | 2 |

|

|

|

|

|

|

10 | LVDS_Y2P | Data Positive Output |

|

|

|

|

|

|

|

11 | LVDS_CLKYM | Clock Negative Output | Clock |

|

12 | LVDS_CLKYP | Clock Positive Output |

|

|

|

|

|

|

|

13 | LVDS_Z0M | Data Negative Output | 0 |

|

14 | LVDS_Z0P | Data Positive Output |

|

|

|

|

|

|

|

15 | LVDS_Z1M | Data Negative Output | 1 |

|

|

|

|

|

|

16 | LVDS_Z1P | Data Positive Output |

| Channel 2 |

|

|

|

|

|

17 | LVDS_Z2M | Data Negative Output | 2 |

|

|

|

|

|

|

18 | LVDS_Z2P | Data Positive Output |

|

|

|

|

|

|

|

19 | LVDS_CLKZM | Clock Negative Output | Clock |

|

|

|

|

|

|

20 | LVDS_CLKZP | Clock Positive Output |

|

|

|

|

|

|

|

Notes: The shaded area denotes power or ground.

NOTE | Pins |

| single channel interface. Pins |

| interface of a two channel interface. |

|

|

48 | Reference Manual | ReadyBoard 700 |