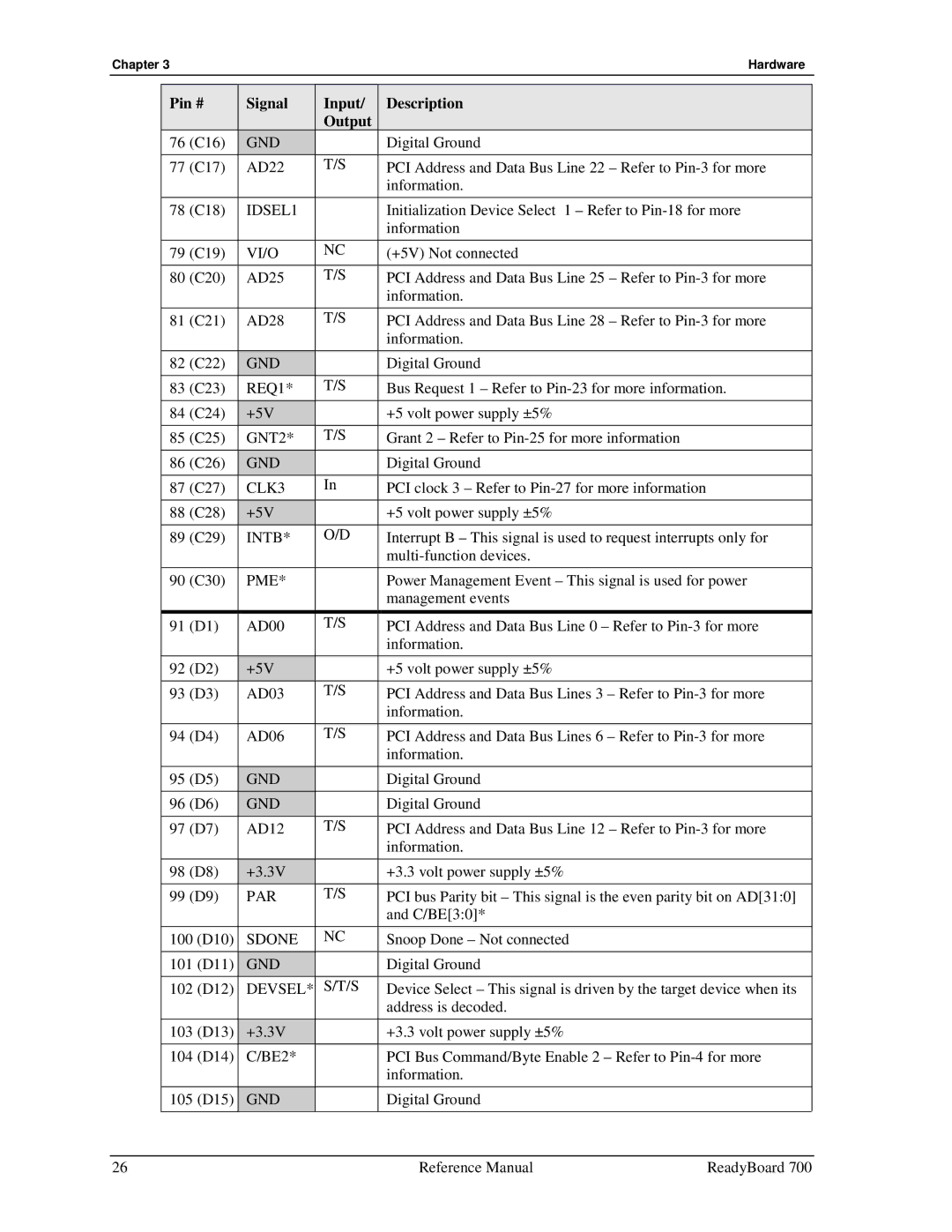

Chapter 3 | Hardware |

Pin # | Signal | Input/ | Description | |

|

|

| Output |

|

76 | (C16) | GND |

| Digital Ground |

77 | (C17) | AD22 | T/S | PCI Address and Data Bus Line 22 – Refer to |

|

|

|

| information. |

78 | (C18) | IDSEL1 |

| Initialization Device Select 1 – Refer to |

|

|

|

| information |

79 | (C19) | VI/O | NC | (+5V) Not connected |

|

|

|

|

|

80 | (C20) | AD25 | T/S | PCI Address and Data Bus Line 25 – Refer to |

|

|

|

| information. |

81 | (C21) | AD28 | T/S | PCI Address and Data Bus Line 28 – Refer to |

|

|

|

| information. |

82 | (C22) | GND |

| Digital Ground |

83 | (C23) | REQ1* | T/S | Bus Request 1 – Refer to |

|

|

|

|

|

84 | (C24) | +5V |

| +5 volt power supply ±5% |

85 | (C25) | GNT2* | T/S | Grant 2 – Refer to |

|

|

|

|

|

86 | (C26) | GND |

| Digital Ground |

87 | (C27) | CLK3 | In | PCI clock 3 – Refer to |

|

|

|

|

|

88 | (C28) | +5V |

| +5 volt power supply ±5% |

89 | (C29) | INTB* | O/D | Interrupt B – This signal is used to request interrupts only for |

|

|

|

| |

90 | (C30) | PME* |

| Power Management Event – This signal is used for power |

|

|

|

| management events |

91 | (D1) | AD00 | T/S | PCI Address and Data Bus Line 0 – Refer to |

|

|

|

| information. |

92 | (D2) | +5V |

| +5 volt power supply ±5% |

93 | (D3) | AD03 | T/S | PCI Address and Data Bus Lines 3 – Refer to |

|

|

|

| information. |

94 | (D4) | AD06 | T/S | PCI Address and Data Bus Lines 6 – Refer to |

|

|

|

| information. |

95 | (D5) | GND |

| Digital Ground |

96 | (D6) | GND |

| Digital Ground |

97 | (D7) | AD12 | T/S | PCI Address and Data Bus Line 12 – Refer to |

|

|

|

| information. |

98 | (D8) | +3.3V |

| +3.3 volt power supply ±5% |

99 | (D9) | PAR | T/S | PCI bus Parity bit – This signal is the even parity bit on AD[31:0] |

|

|

|

| and C/BE[3:0]* |

100 (D10) | SDONE | NC | Snoop Done – Not connected | |

|

|

|

| |

101 (D11) | GND |

| Digital Ground | |

102 (D12) | DEVSEL* | S/T/S | Device Select – This signal is driven by the target device when its | |

|

|

|

| address is decoded. |

103 (D13) | +3.3V |

| +3.3 volt power supply ±5% | |

104 (D14) | C/BE2* |

| PCI Bus Command/Byte Enable 2 – Refer to | |

|

|

|

| information. |

105 (D15) | GND |

| Digital Ground | |

26 | Reference Manual | ReadyBoard 700 |