6.1.1Response to power-on

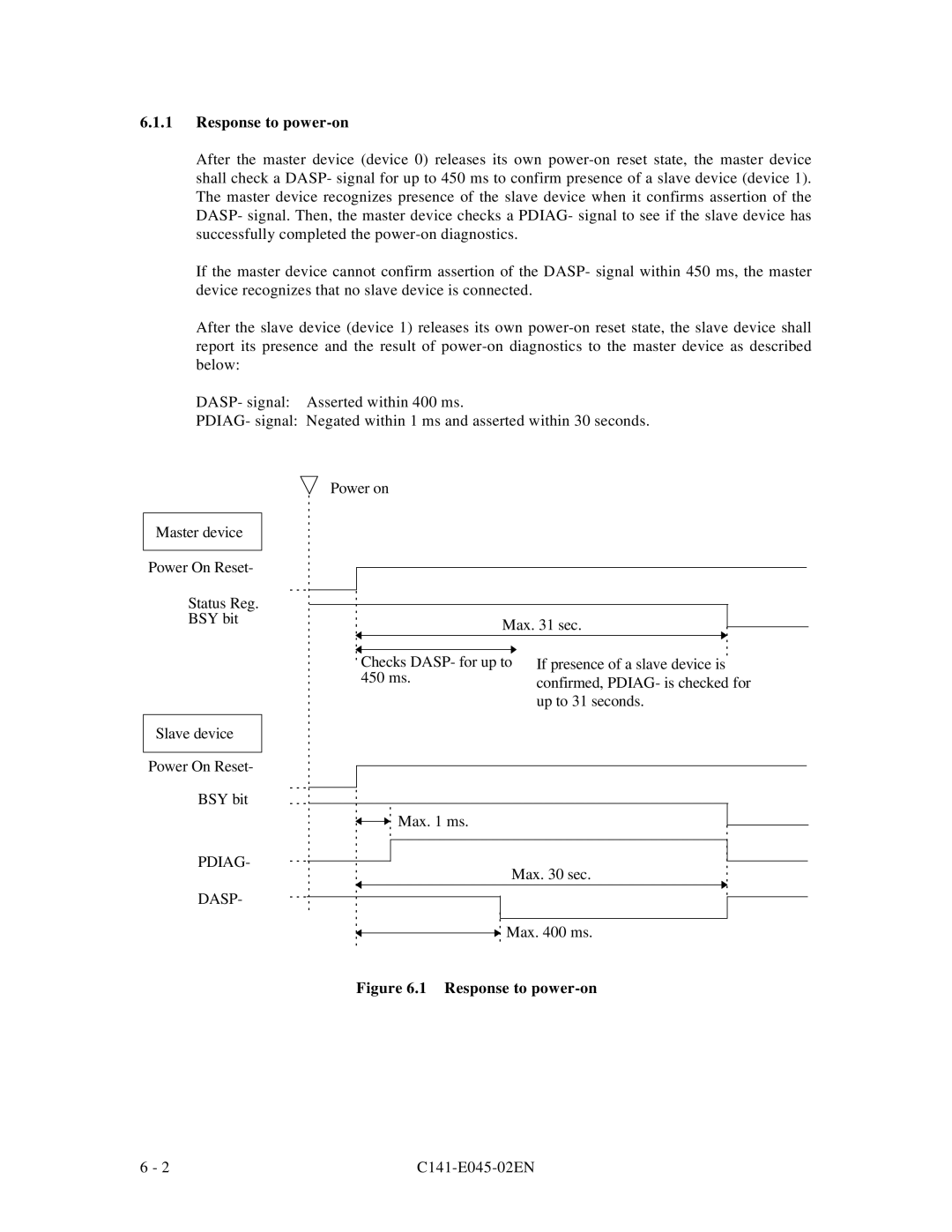

After the master device (device 0) releases its own

If the master device cannot confirm assertion of the DASP- signal within 450 ms, the master device recognizes that no slave device is connected.

After the slave device (device 1) releases its own

DASP- signal:

PDIAG- signal:

Master device

Power On Reset-

Status Reg.

BSY bit

Asserted within 400 ms.

Negated within 1 ms and asserted within 30 seconds.

Power on

Max. 31 sec.

Checks DASP- for up to | If presence of a slave device is |

450 ms. | confirmed, PDIAG- is checked for |

| up to 31 seconds. |

Slave device

Power On Reset-

BSY bit

Max. 1 ms.

PDIAG-

Max. 30 sec.

DASP-

![]() Max. 400 ms.

Max. 400 ms.

Figure 6.1 Response to power-on

6 - 2 |