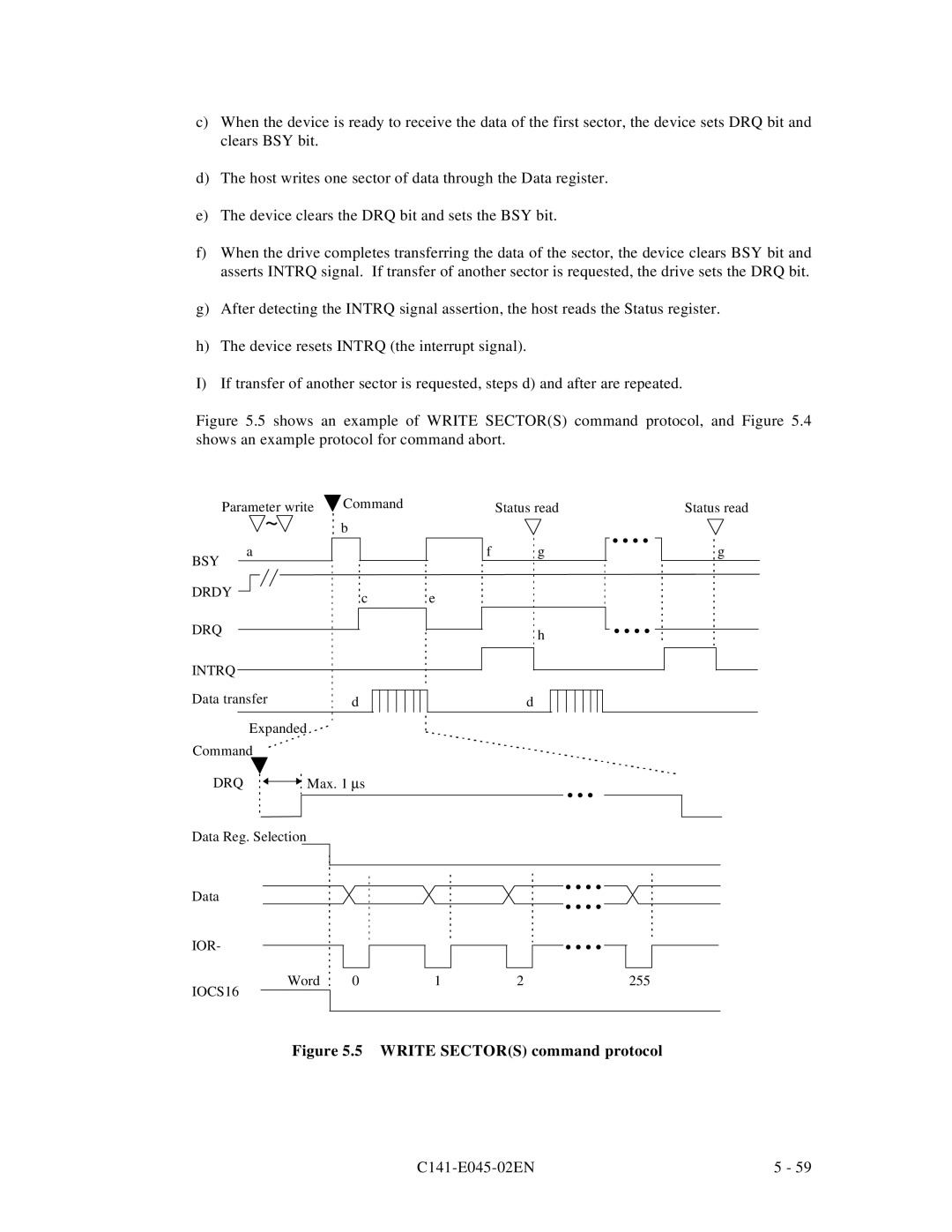

c)When the device is ready to receive the data of the first sector, the device sets DRQ bit and clears BSY bit.

d)The host writes one sector of data through the Data register.

e)The device clears the DRQ bit and sets the BSY bit.

f)When the drive completes transferring the data of the sector, the device clears BSY bit and asserts INTRQ signal. If transfer of another sector is requested, the drive sets the DRQ bit.

g)After detecting the INTRQ signal assertion, the host reads the Status register.

h)The device resets INTRQ (the interrupt signal).

I) If transfer of another sector is requested, steps d) and after are repeated.

Figure 5.5 shows an example of WRITE SECTOR(S) command protocol, and Figure 5.4 shows an example protocol for command abort.

Parameter write | Command | Status read | Status read |

~ | b |

|

|

| a | f | g | • • • • |

BSY | g | |||

|

|

|

| |

DRDY | c | e |

|

|

|

|

| ||

DRQ |

|

| h | • • • • |

INTRQ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

Data transfer |

|

|

|

|

|

|

|

| ||||

d |

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

| |

| Expanded |

| ||||||||||

Command |

|

|

|

|

|

|

|

|

|

| ||

DRQ |

| Max. 1 μs |

| |||||||||

|

| |||||||||||

d

• • •

Data Reg. Selection

Data

IOR-

Word | 0 | 1 |

IOCS16

• • • •

• • • •

![]() • • • •

• • • • ![]()

2255

Figure 5.5 WRITE SECTOR(S) command protocol

5 - 59 |