2 |

CPU Architecture

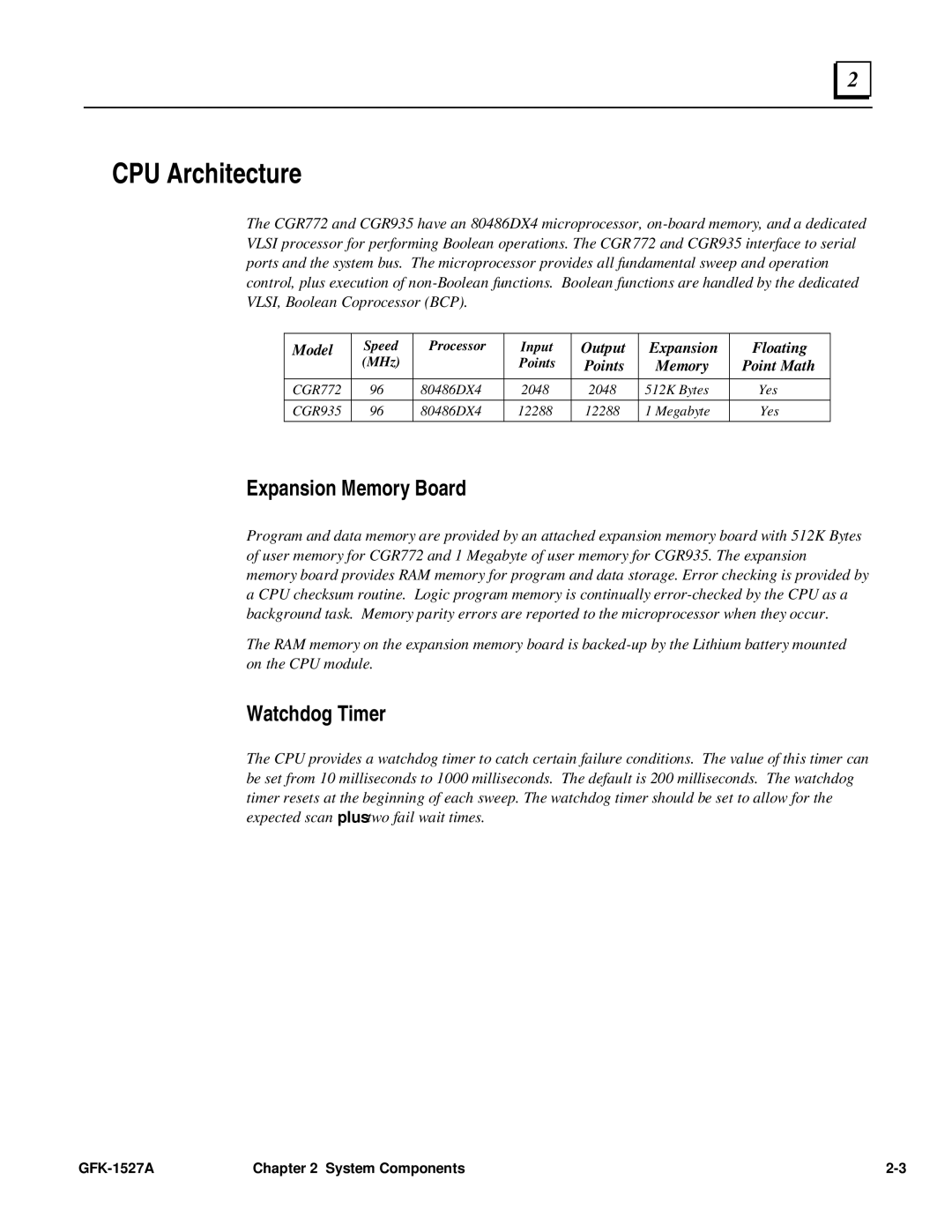

The CGR772 and CGR935 have an 80486DX4 microprocessor,

Model | Speed | Processor | Input | Output | Expansion | Floating |

| (MHz) |

| Points | Points | Memory | Point Math |

|

|

|

|

|

|

|

CGR772 | 96 | 80486DX4 | 2048 | 2048 | 512K Bytes | Yes |

|

|

|

|

|

|

|

CGR935 | 96 | 80486DX4 | 12288 | 12288 | 1 Megabyte | Yes |

|

|

|

|

|

|

|

Expansion Memory Board

Program and data memory are provided by an attached expansion memory board with 512K Bytes of user memory for CGR772 and 1 Megabyte of user memory for CGR935. The expansion memory board provides RAM memory for program and data storage. Error checking is provided by a CPU checksum routine. Logic program memory is continually

The RAM memory on the expansion memory board is

Watchdog Timer

The CPU provides a watchdog timer to catch certain failure conditions. The value of this timer can be set from 10 milliseconds to 1000 milliseconds. The default is 200 milliseconds. The watchdog timer resets at the beginning of each sweep. The watchdog timer should be set to allow for the expected scan plus two fail wait times.

Chapter 2 System Components |